支持蓝牙BLE协议的射频收发器及其控制方法.pdf

羽沫****魔王

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

支持蓝牙BLE协议的射频收发器及其控制方法.pdf

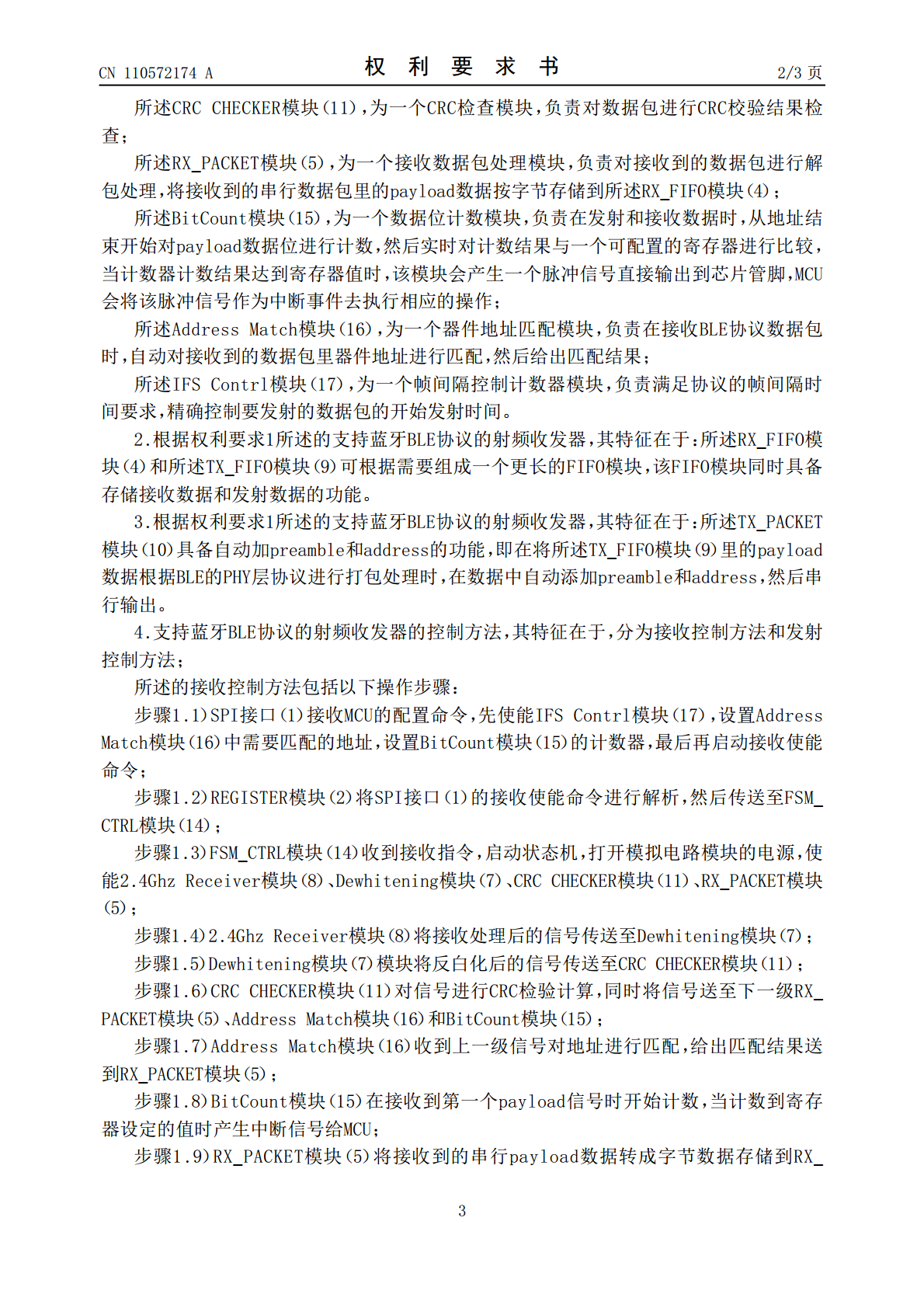

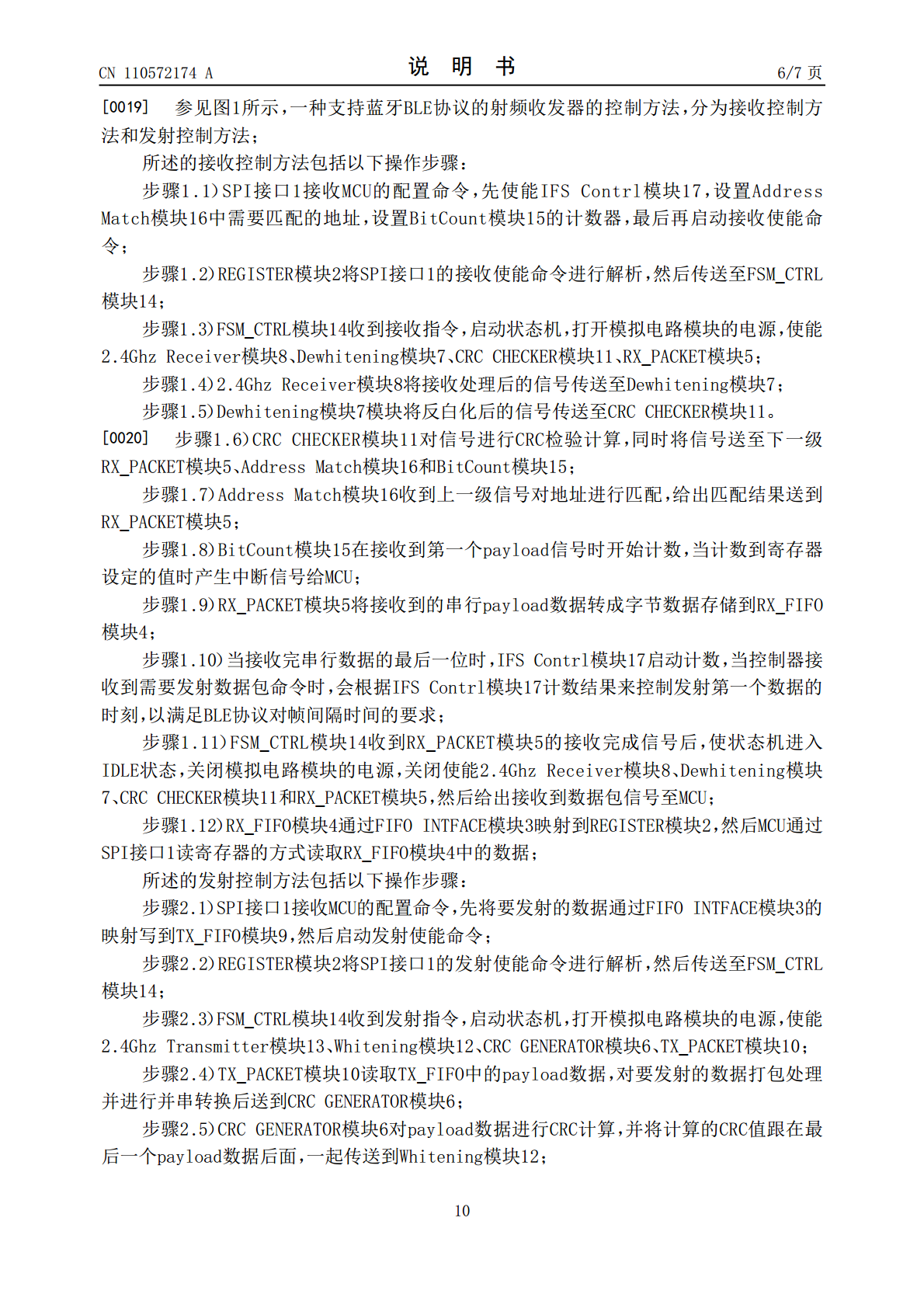

本发明公开了一种支持蓝牙BLE协议的射频收发器及其控制方法,该收发器通过在通用的2.4Ghz射频收发器中内置部分需要快速数据控制的BLE协议模块,让射频收发器实现部分协议链接层的工作,减小射频收发器和MCU之间的数据量,MCU可直接通过SPI接口控制射频收发器以实现BLE协议的控制,使得在设计BLE芯片时不受MCU限制,只需考虑射频收发器的性能和功能的实现。相比于传统的SOC解决方案,本发明对于蓝牙射频收发器的物理层和协议层做了清晰地分割,能够通过SPI接口满足蓝牙协议中的关键收发时间窗口要求,且设计灵活

蓝牙BLE智能灯.ppt

联客智能产品介绍智能灯产品------产品资源智能灯产品------应用环境智能灯产品------应用和功能(1)智能灯产品------应用和功能(2)智能灯产品------应用和功能(3)智能灯产品------应用和功能(4)智能灯产品------应用和功能(5)智能灯产品------应用和功能(6)智能灯产品------应用和功能(7)智能灯产品------应用和功能(8)www.linkiing.com

一种射频开关控制方法、装置及射频收发器.pdf

本发明提供了一种射频开关控制方法、装置及射频收发器,本发明中的与射频收发器连接的射频开关的开关切换时间小于预设开关切换时间、且当前射频开关再次连通时,该当前射频开关就可以正常使用,保证本发明中的天线阵列能够满足规定的天线切换时槽要求。在满足要求的基础上,相邻两级射频开关的开关切换时间满足预设切换时间关联关系,即不需要所有的射频开关的开关切换时间均满足对应的天线切换时槽要求,也就是说,允许除了与射频收发器连接的射频开关之外的其他射频开关的开关切换时间不满足对应的天线切换时槽要求,降低了对射频开关的开关切换时

医疗装置射频收发器及其使用方法.pdf

本文描述了射频(RF)收发器,其充当中继装置,以在医疗装置(例如,植入体内的医疗装置)的传感器与外围装置(诸如智能手机)之间提供通信。所述医疗装置可以为尿道内、直肠内或阴道内装置。所述医疗装置的所述传感器可以为微机电(MEM)传感器,诸如加速度计。

基于BLE蓝牙的LED灯音乐律动系统、控制方法及装置.pdf

本发明涉及一种基于BLE蓝牙的LED灯音乐律动系统、控制方法及装置,所述系统包括LED灯带以及与LED灯带电连接的BLE蓝牙模块;BLE蓝牙模块包括无线接收组件以及与无线接收组件电连接的BLE蓝牙芯片,BLE蓝牙芯片与LED灯带电连接;无线接收组件接收外部音源设备发送的LED闪烁图信息,并将所述LED闪烁图信息发送给BLE蓝牙芯片,所述LED闪烁图信息为所述外部音源设备根据当前播放的歌曲的频谱信息所生成的;BLE蓝牙芯片根据LED闪烁图信息控制LED灯带进行闪烁。本发明实施例通过采用BLE蓝牙模块接收外部