一种基于硬件电路实现485收发自动切换的实现方法.pdf

猫巷****觅蓉

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种基于硬件电路实现485收发自动切换的实现方法.pdf

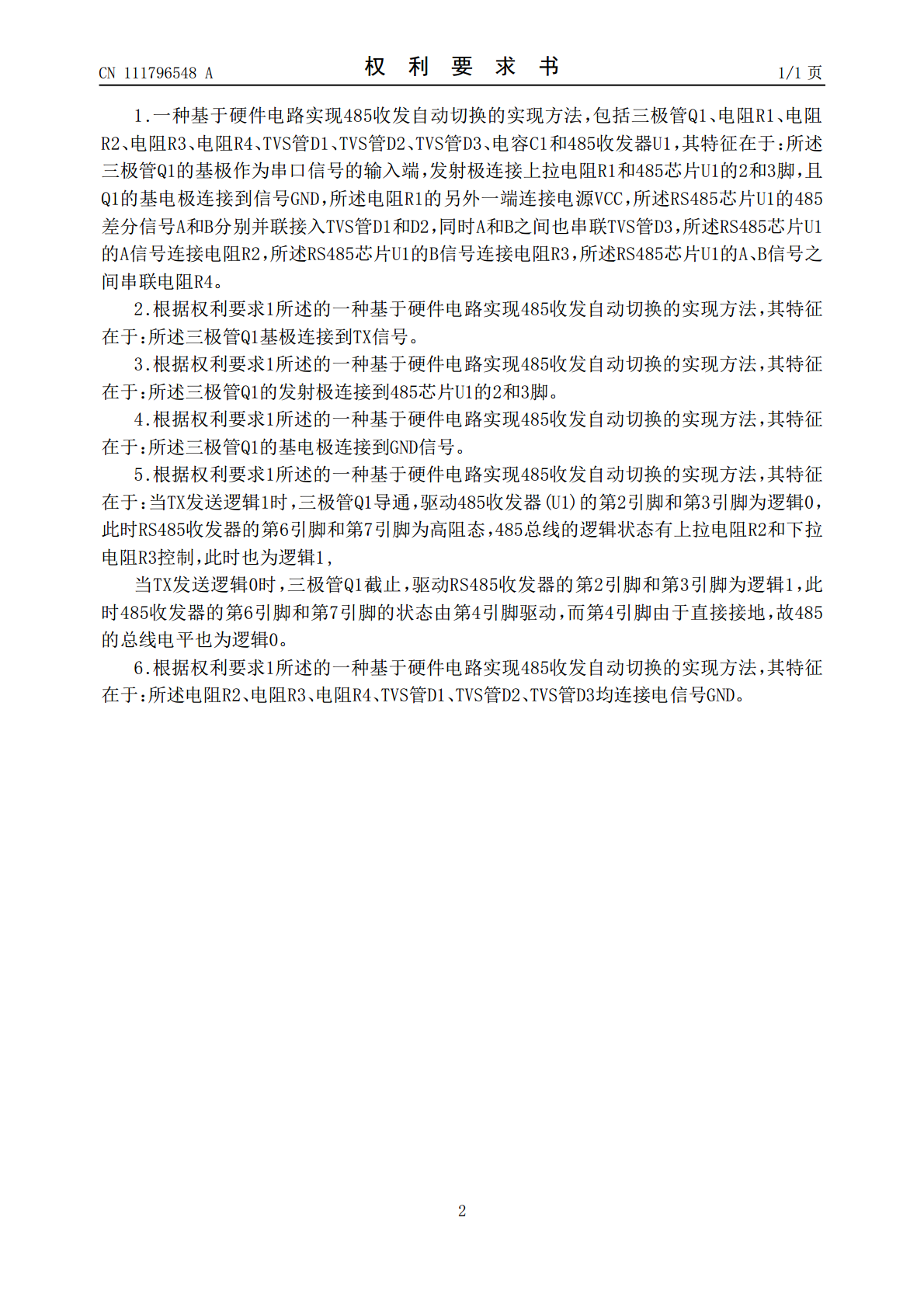

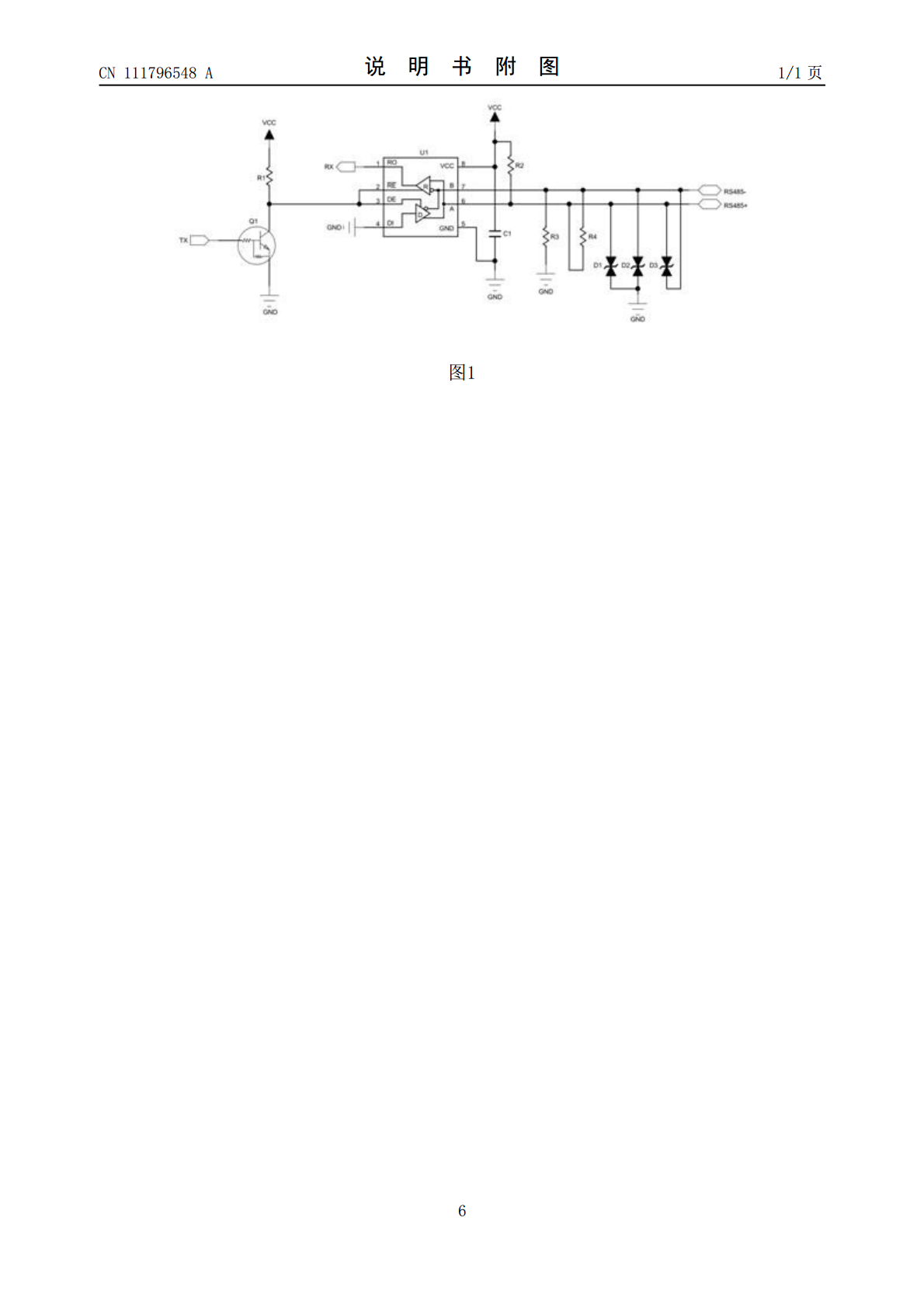

本发明公开了一种基于硬件电路实现485收发自动切换的实现方法,包括三极管Q1、电阻R1、电阻R2、电阻R3、电阻R4、TVS管D1、TVS管D2、TVS管D3、电容C1和485收发器U1,本发明无需修改现有软件,轻松实现485相关功能;由于通过IO口软件切换收发控制存在延时,导致响应速度不够,所以本专利存在收发控制切换速度快的特点;由于本方案只需要增加一个三极管和一个电阻,相比其他硬件方案具有成本低的优点;于使用的是硬件485切换电路,具有可靠性高的优点;开发速度快。

一种实现车载外部音频通道自动切换的电路及方法.pdf

本发明公开了一种实现车载外部音频通道自动切换的电路及方法,利用倍压整流电路的倍压整流特性以及三极管的结构特性和不同工作状态下的电流特征,通过采用I2C通信以及A/D采集的方式,来实现车载外部音频通道的自动切换;本发明的自动切换电路和方法可以应用到含有外部音频输入功能的车载多媒体终端设备中,用来实现外部音频通道的自动切换,使得驾驶员在安全驾驶的前提下可以随时聆听手机等设备的音乐;本发明在相对比较微弱的外部音频信号也能实现自动检测以及进行音频通道的自动切换,具有检测精度高的优点。

基于FPGA的组合逻辑电路自动合成的硬件实现.docx

基于FPGA的组合逻辑电路自动合成的硬件实现引言组合逻辑电路自动合成是数字集成电路设计中的重要一环。现在的数字电路设计往往需要处理复杂的逻辑,这些逻辑可能包含大量的布尔运算,并且需要在极短的时间内完成计算,因此使用硬件实现是必须的。组合逻辑电路是一种由若干输入和输出变量组成的电路,其中每个输出变量只依赖于输入变量和电路中的内部变量。在这种电路中,输入信号会立即被转化为相应的输出信号,故称为组合逻辑电路。在本文中,我们将探讨基于FPGA的组合逻辑电路自动合成的硬件实现。背景知识FPGA(FieldProgr

一种RS485自动收发隔离电路.pdf

本发明提供一种RS485自动收发隔离电路,包括隔离供电电源电路为内部通讯电路提供隔离的电源,实现内外部收发器电源与地的完全隔离;RS485通讯隔离电路实现内外部RS485总线数据转换和隔离;RS485数据流向控制电路实现无CPU控制时,通讯链路数据流向的自动转换;RS485接口雷电防护电路用于抑制瞬态差共模高电压,对RS485通讯协议芯片U2、U3进行有效防护。本发明简化了RS485通讯隔离电路中数据流向CPU控制需求,借助高速NPN型三极管可实现通讯数据的零延时隔离;借助RS485通讯芯片和磁耦隔离芯片

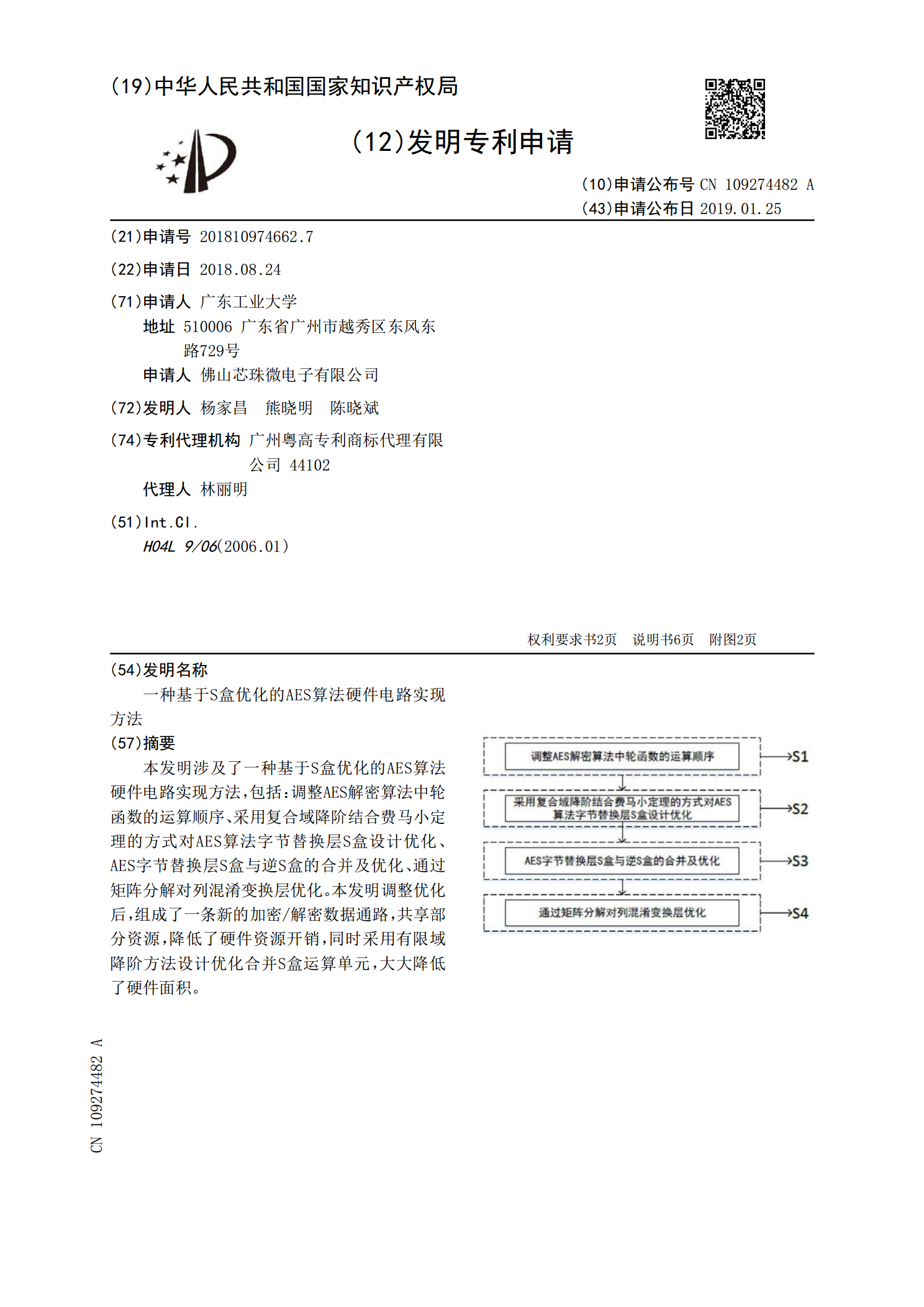

一种基于S盒优化的AES算法硬件电路实现方法.pdf

本发明涉及了一种基于S盒优化的AES算法硬件电路实现方法,包括:调整AES解密算法中轮函数的运算顺序、采用复合域降阶结合费马小定理的方式对AES算法字节替换层S盒设计优化、AES字节替换层S盒与逆S盒的合并及优化、通过矩阵分解对列混淆变换层优化。本发明调整优化后,组成了一条新的加密/解密数据通路,共享部分资源,降低了硬件资源开销,同时采用有限域降阶方法设计优化合并S盒运算单元,大大降低了硬件面积。