存储器接口、数据存储设备及其操作方法.pdf

书生****66

亲,该文档总共31页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

存储器接口、数据存储设备及其操作方法.pdf

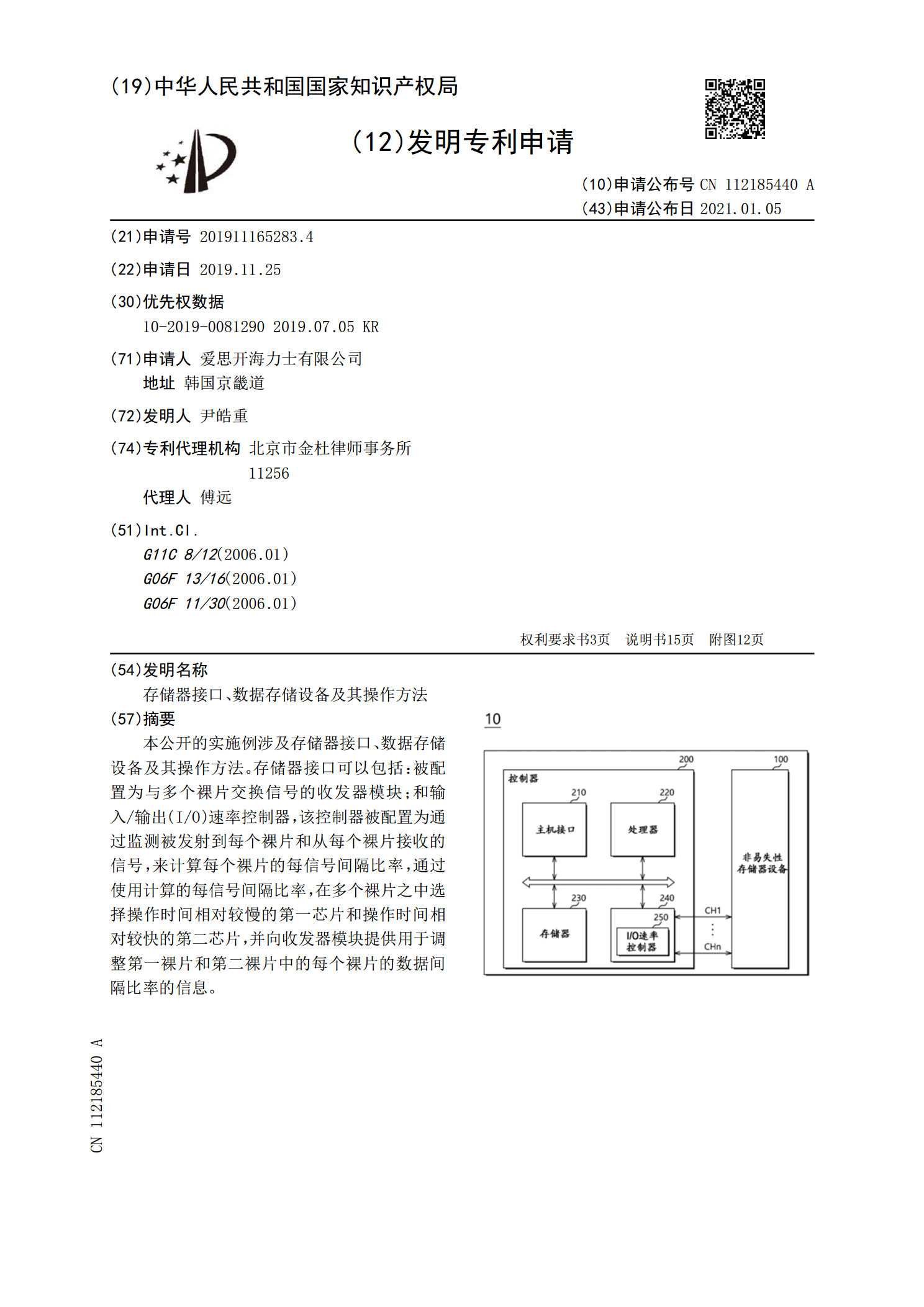

本公开的实施例涉及存储器接口、数据存储设备及其操作方法。存储器接口可以包括:被配置为与多个裸片交换信号的收发器模块;和输入/输出(I/O)速率控制器,该控制器被配置为通过监测被发射到每个裸片和从每个裸片接收的信号,来计算每个裸片的每信号间隔比率,通过使用计算的每信号间隔比率,在多个裸片之中选择操作时间相对较慢的第一芯片和操作时间相对较快的第二芯片,并向收发器模块提供用于调整第一裸片和第二裸片中的每个裸片的数据间隔比率的信息。

存储器设备及其操作方法.pdf

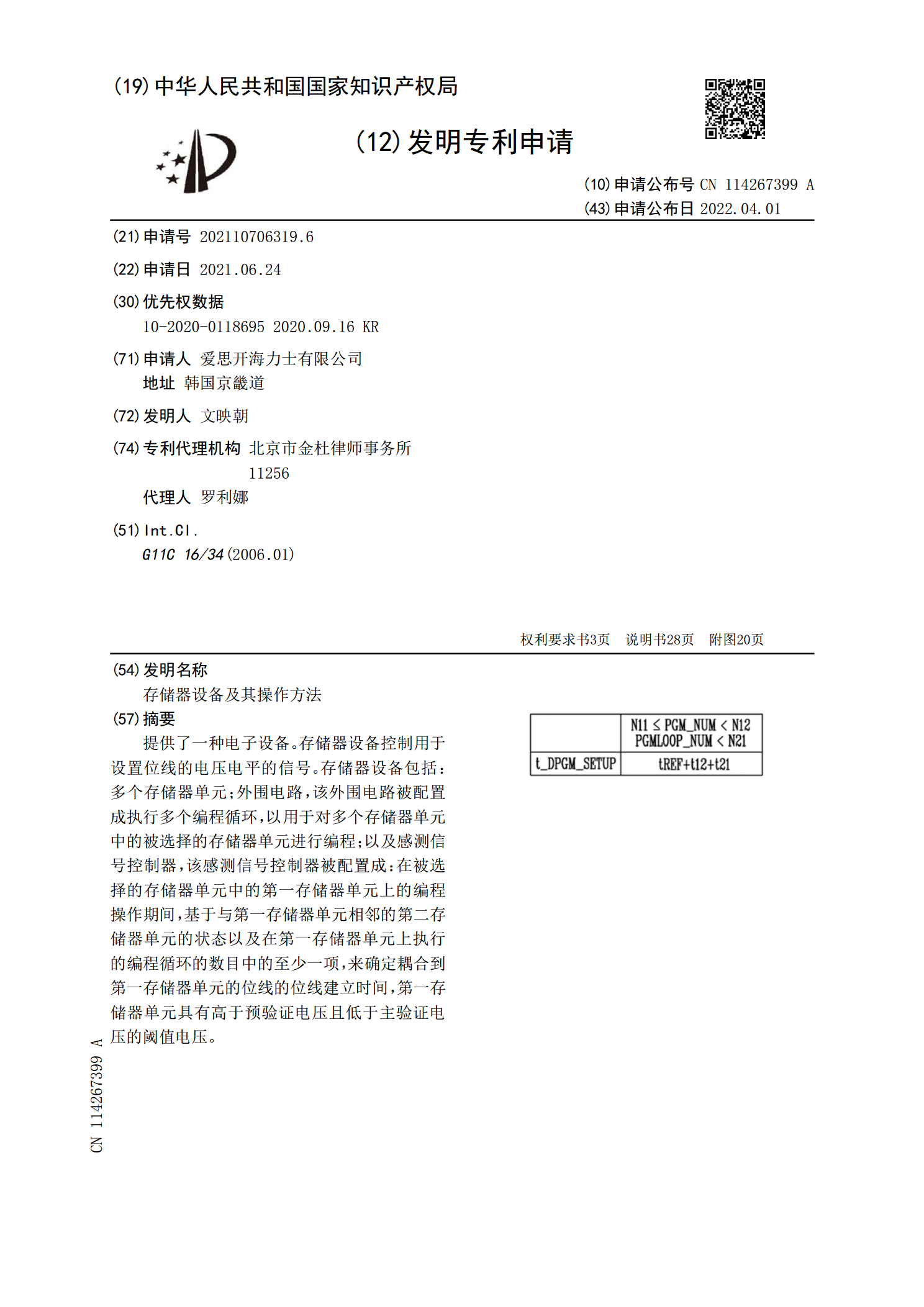

提供了一种电子设备。存储器设备控制用于设置位线的电压电平的信号。存储器设备包括:多个存储器单元;外围电路,该外围电路被配置成执行多个编程循环,以用于对多个存储器单元中的被选择的存储器单元进行编程;以及感测信号控制器,该感测信号控制器被配置成:在被选择的存储器单元中的第一存储器单元上的编程操作期间,基于与第一存储器单元相邻的第二存储器单元的状态以及在第一存储器单元上执行的编程循环的数目中的至少一项,来确定耦合到第一存储器单元的位线的位线建立时间,第一存储器单元具有高于预验证电压且低于主验证电压的阈值电压。

存储器设备及其操作方法.pdf

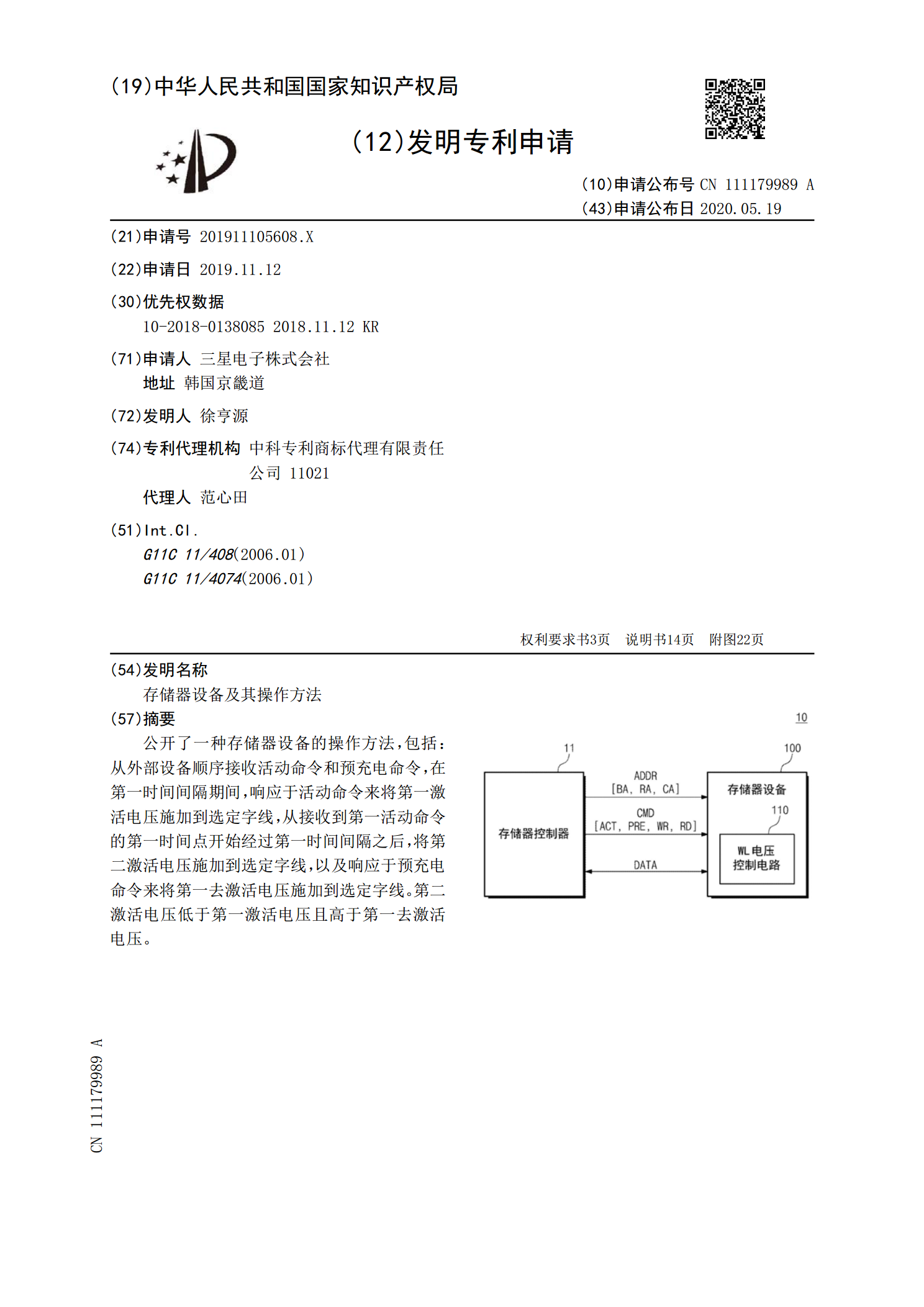

公开了一种存储器设备的操作方法,包括:从外部设备顺序接收活动命令和预充电命令,在第一时间间隔期间,响应于活动命令来将第一激活电压施加到选定字线,从接收到第一活动命令的第一时间点开始经过第一时间间隔之后,将第二激活电压施加到选定字线,以及响应于预充电命令来将第一去激活电压施加到选定字线。第二激活电压低于第一激活电压且高于第一去激活电压。

存储器及其接口.ppt

第三章存储器及其接口3.1概述3.1.2存储设备的分类3.2半导体存储器3.2.1易失性存储器1静态随机存取储存器(SRAM)2动态存储器DRAM3伪静态随机存储器PSRAM3.2.2非易失性存储器1只读存储器ROM2一次性编程的OTPROM3可多次编程写入的只读存储器4Flash存储器5铁电存储器FRAM3.3内存的管理2保护虚地址模式地址转换3.3.2PC系列微机的存储器空间(1)基本内存(2)上位内存(UpperMemory)(3)扩展内存(ExtendedMemory)(4)扩充内存3.3.3常规

存储器及其接口.ppt

第5章存储器及其接口5.1存储器的概念、分类和要素5.1.1简介5.1.2半导体存储器的分类1.按使用元件分类2.从应用角度分类说明5.1.3选择存储器件的考虑因素5.2内存储器5.2.1随机读写存储器(RAM)1.RAM的基本结构及组成RAM的组成RAM的结构框图2.静态RAMT1、T2为工作管,T3、T4是负载管,T5、T6、T7、T8是控制管。该电路有两种稳定状态:T1截止,T2导通为状态“1”;T2截止,T1导通为状态“0”。CMOS的基本存储电路SRAM芯片应用SRAM芯片应用3.动态RAMDR