基于FPGA的HDLC协议实现.pdf

qw****27

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于FPGA的HDLC协议实现.pdf

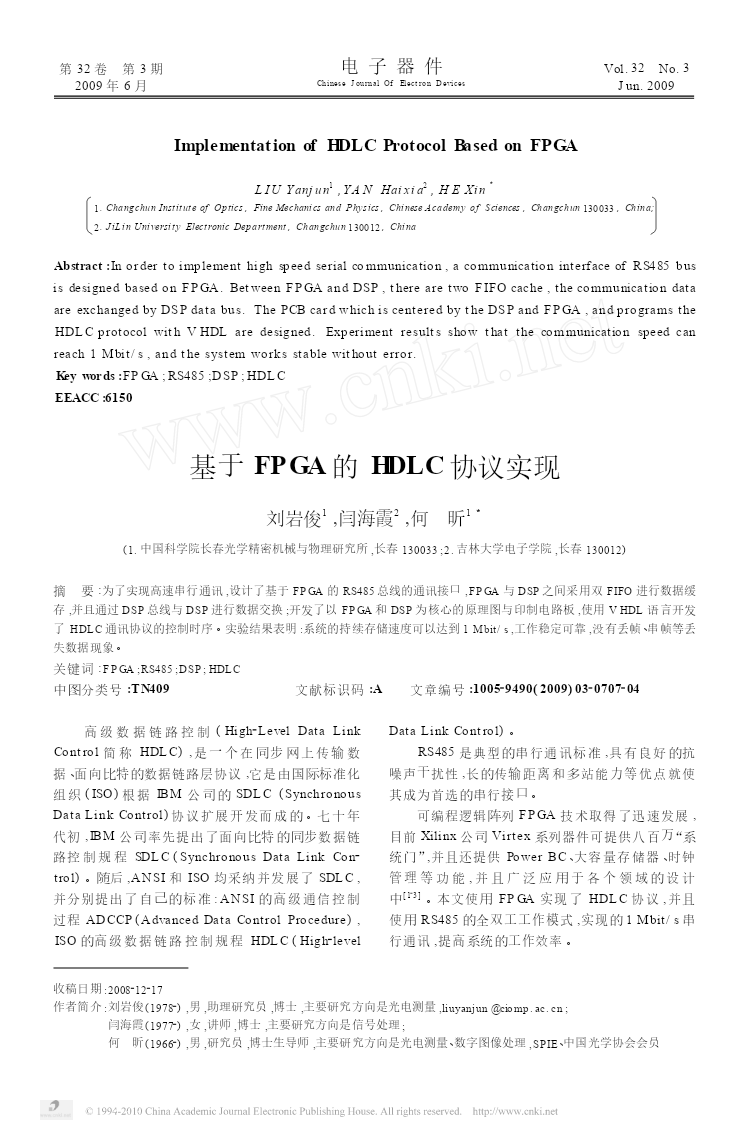

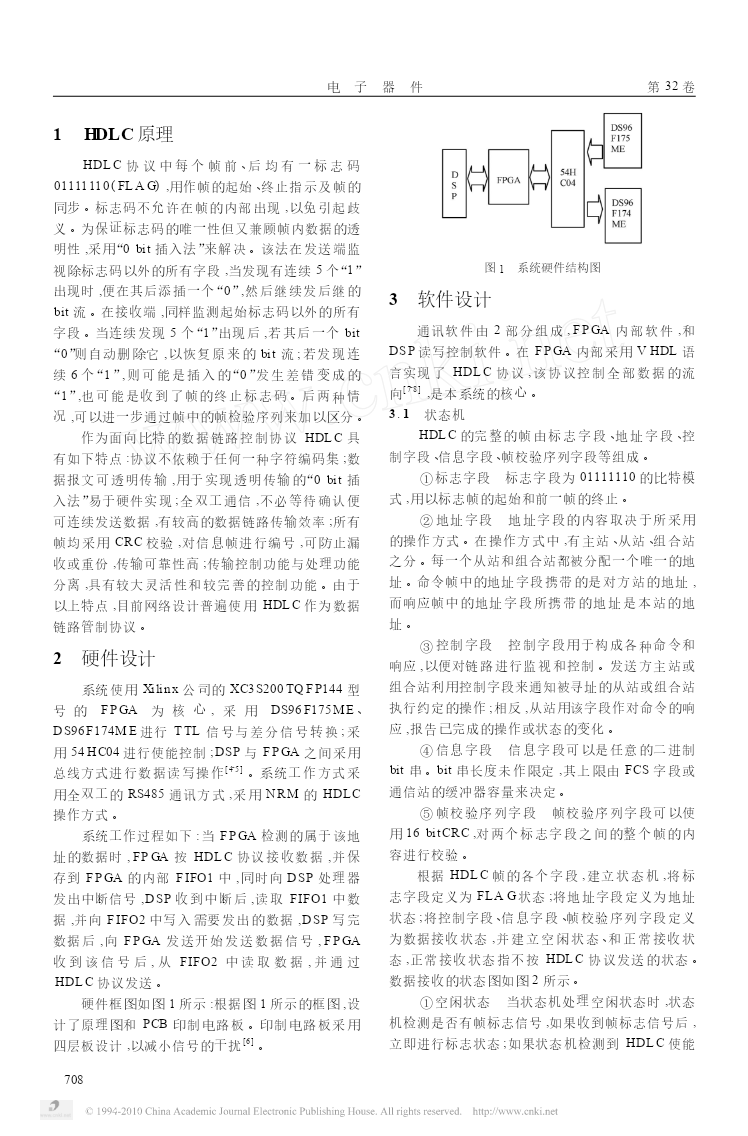

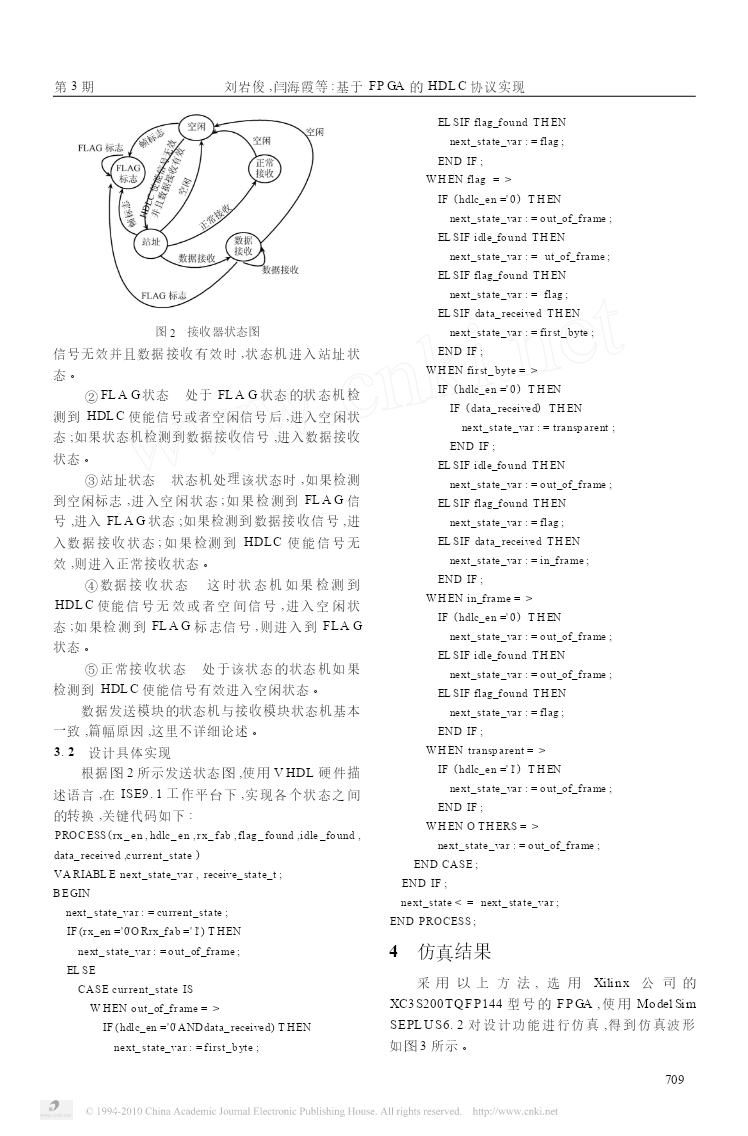

第卷第期电子器件323Vol.32No.32009年6月ChineseJournalOfElectronDevicesJun.2009ImplementationofHDLCProtocolBasedonFPGALIUYanjun1,YANHaixia2,HEXin31.ChangchunInstituteofOptics,FineMechanicsandPhysics,ChineseAcademyofSciences,Changchun130033,China;2.JiLinUniversityElec

基于FPGA的HDLC协议的设计与实现.pdf

第卷第期电子器件323Vol.32No.32009年6月ChineseJournalOfElectronDevicesJun.2009DesignandImplementationofHDLCProceduresBasedonFPGAZHANGWenhao,WANGJun3,YUPengfei,WUWei(SchoolofElectronicandInformationEngineering,BeihangUniversity,Beijing100191,China)Abstract:High2level

基于FPGA的HDLC通信模块的实现.docx

基于FPGA的HDLC通信模块的实现基于FPGA的HDLC通信模块的实现基于FPGA的HDLC通信模块的实现摘要:本文设计了一种基于FPGA的HDLC通信模块,并在FPGA上成功实现功能。HDLC(HighLevelDataLinkControl)协议是通信领域中应用最广泛的协议之一,它是面向比特的高级数据链路控制规程,具有差错检测功能强大、高效和同步传输的'特点。HDLC是面向位的,这意味着数据是一位一位地监控的,传输的数据以二进制数据组成,不存在任何特殊的控制代码,但帧中的信息包含了控制和响应命令。H

基于FPGA的HDLC通信模块的实现.docx

基于FPGA的HDLC通信模块的实现基于FPGA的HDLC通信模块的实现基于FPGA的HDLC通信模块的实现摘要:本文设计了一种基于FPGA的HDLC通信模块,并在FPGA上成功实现功能。HDLC(HighLevelDataLinkControl)协议是通信领域中应用最广泛的协议之一,它是面向比特的高级数据链路控制规程,具有差错检测功能强大、高效和同步传输的'特点。HDLC是面向位的,这意味着数据是一位一位地监控的,传输的数据以二进制数据组成,不存在任何特殊的控制代码,但帧中的信息包含了控制和响应命令。H

基于FPGA的HDLC通信模块的实现.docx

基于FPGA的HDLC通信模块的实现基于FPGA的HDLC通信模块的实现基于FPGA的HDLC通信模块的实现摘要:本文设计了一种基于FPGA的HDLC通信模块,并在FPGA上成功实现功能。HDLC(HighLevelDataLinkControl)协议是通信领域中应用最广泛的协议之一,它是面向比特的高级数据链路控制规程,具有差错检测功能强大、高效和同步传输的'特点。HDLC是面向位的,这意味着数据是一位一位地监控的,传输的数据以二进制数据组成,不存在任何特殊的控制代码,但帧中的信息包含了控制和响应命令。H