发射码元相位调整方法和系统.pdf

雨巷****可歆

亲,该文档总共21页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

发射码元相位调整方法和系统.pdf

本申请实施例公开了一种发射码元相位调整方法和系统,用于调整发射IQ码元相位,实现IQ码元相位对齐。该系统包括FPGA和相位采集模块,FPGA包括锁相环、逻辑单元、第一串行收发器、第二串行收发器和相位控制模块;其中,逻辑单元根据锁相环输出的目标时钟信号,产生数字基带码元信号后,第一串行器收发器和第二串行收发器在数字基带码元信号和目标时钟信号的作用下,分别串行发射出I路和Q路模拟基带码元信号;相位采集模块采集I路和Q路的模拟基带码元信号之间相位信息;相位控制模块在IQ码元相位有偏差时,根据相位信息,调整收发器

CoMP系统中相位调整方法.docx

CoMP系统中相位调整方法相位调整方法在CoMP(协作多点传输)系统中扮演着重要的角色,可以提升系统的容量和覆盖范围。本文将介绍CoMP系统中常用的相位调整方法,并对每种方法进行详细的分析和比较。一、引言CoMP系统是一种利用多个基站协同工作以提高无线通信性能的技术。通过对多个基站之间的协作,可以减小干扰、提高系统容量和覆盖范围。在CoMP系统中,相位调整是一种关键技术,通过调整基站之间的相位差,可以实现干扰抵消和信号增强,从而提高系统性能。二、相位调整方法1.静态相位调整方法静态相位调整方法是指在系统初

一种基于连续相位调制信号相位变化特征的码元同步方法.pdf

本发明公开了一种基于连续相位调制信号相位变化特征的码元同步方法,本发明的主要步骤为:提取同步前导信号的相位变化特征;与本地的同步码做相关运算;找到相关运算峰值的时间位置,完成码元同步。针对现有数字通信系统中码元同步算法过于复杂和消耗硬件资源较多的问题,本发明能准确地确定接收信号码元的起止时刻,运算量少,减轻了系统的运算负担,特别适用于硬件资源紧张的通信系统。而且,本发明能运用于存在多普勒频偏的情况,有效克服多普勒频偏对接收信号码元同步的影响。在较低信噪比的情况下,本发明仍能可靠地实现同步。

B1电控系统相位度数的调整方法.ppt

单点课一:PLC的扫描周期一:PLC的扫描周期一:PLC的扫描周期一:PLC的扫描周期一:PLC的扫描周期二:B1的相位度数调整二:B1的相位度数调整二:B1的相位度数调整二:B1的相位度数调整二:B1的相位度数调整二:B1的相位度数调整二:B1的相位度数调整三:PLC与工控机响应速度的比较三:PLC与工控机响应速度的比较

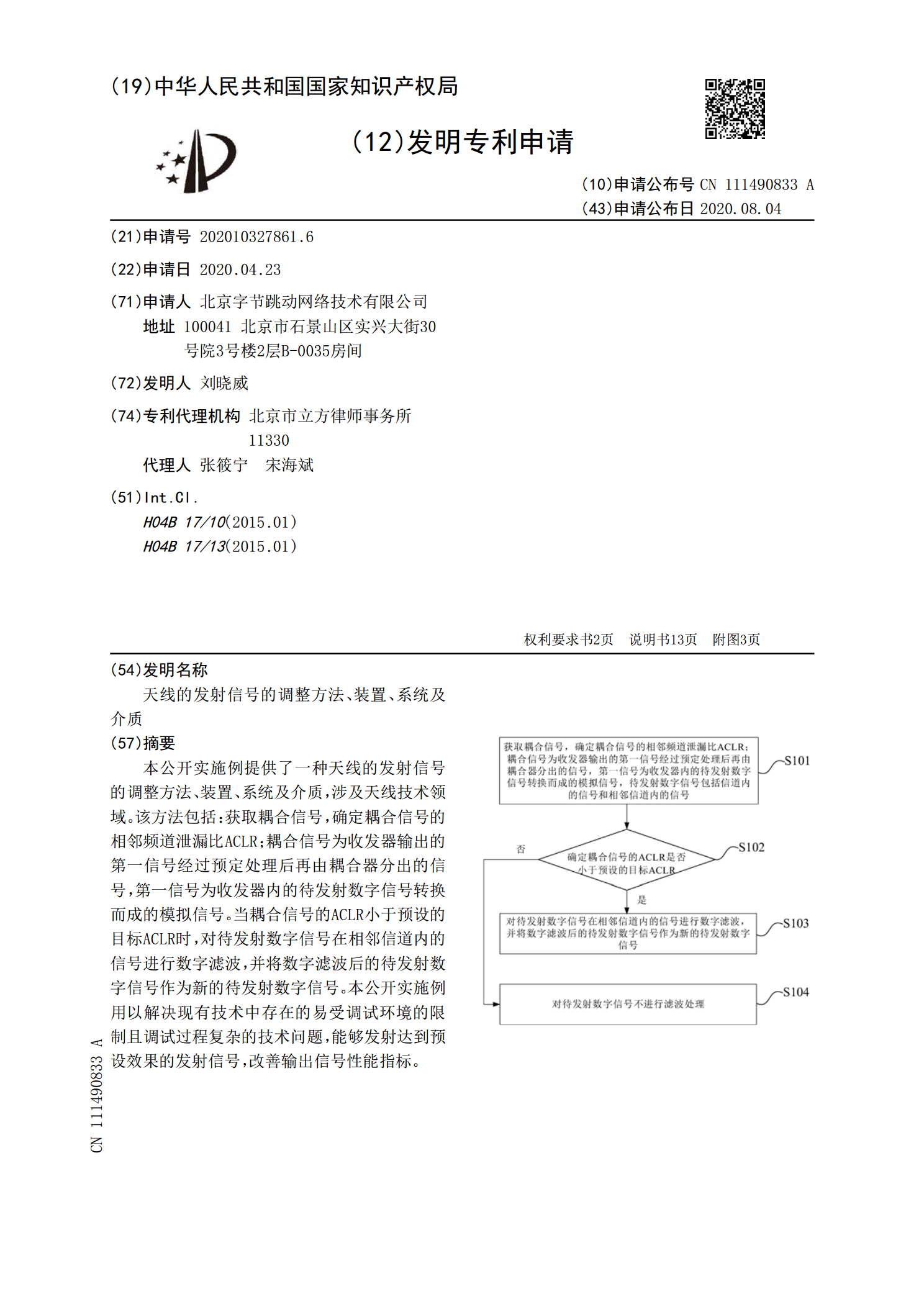

天线的发射信号的调整方法、装置、系统及介质.pdf

本公开实施例提供了一种天线的发射信号的调整方法、装置、系统及介质,涉及天线技术领域。该方法包括:获取耦合信号,确定耦合信号的相邻频道泄漏比ACLR;耦合信号为收发器输出的第一信号经过预定处理后再由耦合器分出的信号,第一信号为收发器内的待发射数字信号转换而成的模拟信号。当耦合信号的ACLR小于预设的目标ACLR时,对待发射数字信号在相邻信道内的信号进行数字滤波,并将数字滤波后的待发射数字信号作为新的待发射数字信号。本公开实施例用以解决现有技术中存在的易受调试环境的限制且调试过程复杂的技术问题,能够发射达到预