基于RapidIO协议的高速实时传输实现系统及方法.pdf

永梅****33

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于RapidIO协议的高速实时传输实现系统及方法.pdf

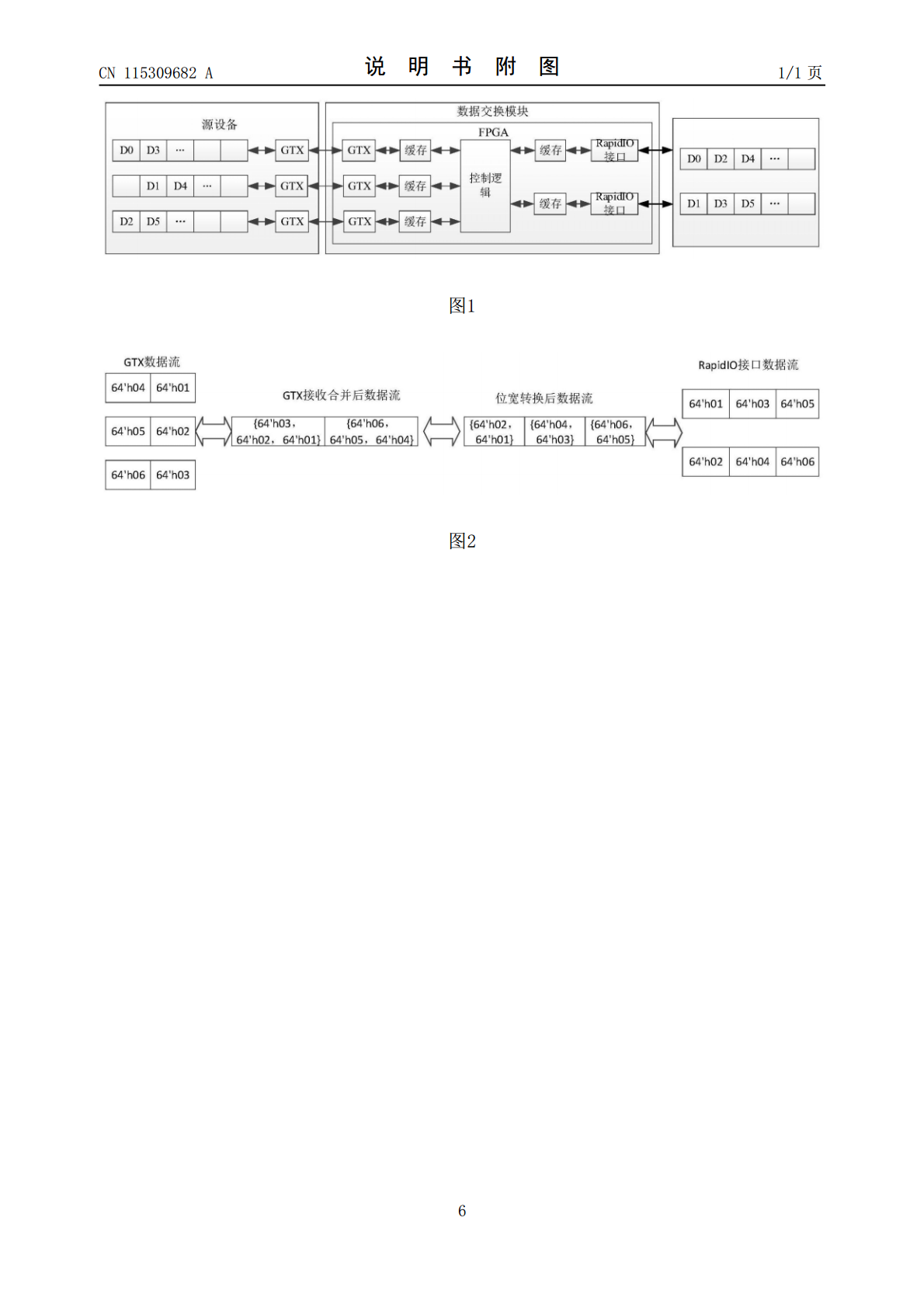

本发明公开了一种基于RapidIO协议的高速实时传输实现系统及方法,包括同时连接源设备和目的设备的数据交换模块,所述数据交换模块包括FPGA芯片,所述源设备与数据交换模块通过串行收发器交互数据,所述数据交换模块与目的设备通过RapidIO接口交互数据,所述串行收发器和RapidIO接口均通过缓存模块与FPGA芯片连接。本发明系统灵活性高、可扩展性强,便于移植。本发明可以根据系统需求增减源设备和数据交换模块FPGA之间的接口、数据交换模块FPGA和目的设备之间的接口,通过接口的增减实现数据传输带宽的调节。本

基于RapidIO的高速传输接口的研究与设计.pptx

添加副标题目录PART01PART02当前通信技术的发展趋势RapidIO技术的重要性和应用领域研究目的和意义PART03RapidIO技术简介RapidIO技术特点与优势RapidIO技术发展历程和现状PART04高速传输接口的技术要求和设计目标硬件接口设计软件接口设计接口性能测试与评估PART05实验环境与测试平台实验过程与测试数据采集实验结果与分析结果对比与性能优化探讨PART06研究成果总结与贡献未来研究方向与展望对RapidIO技术发展的建议和展望感谢您的观看

基于RIP的视频监控图像实时传输系统的设计与实现.docx

基于RIP的视频监控图像实时传输系统的设计与实现视频监控系统已经成为了现代安全防范领域不可缺少的一部分,随着视频监控技术的不断发展,人们对于视频监控系统的要求也越来越高。在视频监控系统中,实时性和稳定性是重要的指标,因为这些指标直接关系到安全领域的实际应用。而大规模视频监控系统中,图像传输的实时性更是考验着整个系统的稳定性和性能。因此,本文基于RIP协议设计了一个视频监控图像实时传输系统,以提高视频图像传输的实时性和系统的稳定性,为用户提供更好的使用体验。一、系统设计本系统采用的是基于RIP协议的视频监控

基于RapidIO协议包交换芯片的实现.pptx

汇报人:CONTENTSPARTONEPARTTWORapidIO协议简介RapidIO协议特点RapidIO协议应用场景PARTTHREE包交换芯片功能包交换芯片设计原理包交换芯片关键技术PARTFOUR芯片总体架构设计芯片模块化设计芯片接口设计芯片性能测试与评估PARTFIVE芯片应用领域芯片优势分析芯片应用前景展望PARTSIX研究成果总结研究不足与展望汇报人:

基于专用芯片的高速实时 FFT 系统实现研究.docx

基于专用芯片的高速实时FFT系统实现研究基于专用芯片的高速实时FFT系统实现研究摘要傅里叶变换(FourierTransform,简称FFT)是一种重要的信号处理技术,在许多领域广泛应用。然而,传统的FFT算法在大规模数据处理中存在计算复杂度高、实时性差等问题。为解决这些问题,本文研究了基于专用芯片的高速实时FFT系统实现方案。首先,介绍了FFT的基本原理和算法流程,并分析了其计算复杂度。然后,通过对比分析了传统CPU实现FFT与基于专用芯片实现FFT的优缺点。接着,详细介绍了基于专用芯片的高速实时FFT