基于复合域循环S盒掩码抗侧信道攻击的AES电路.pdf

努力****星驰

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于复合域循环S盒掩码抗侧信道攻击的AES电路.pdf

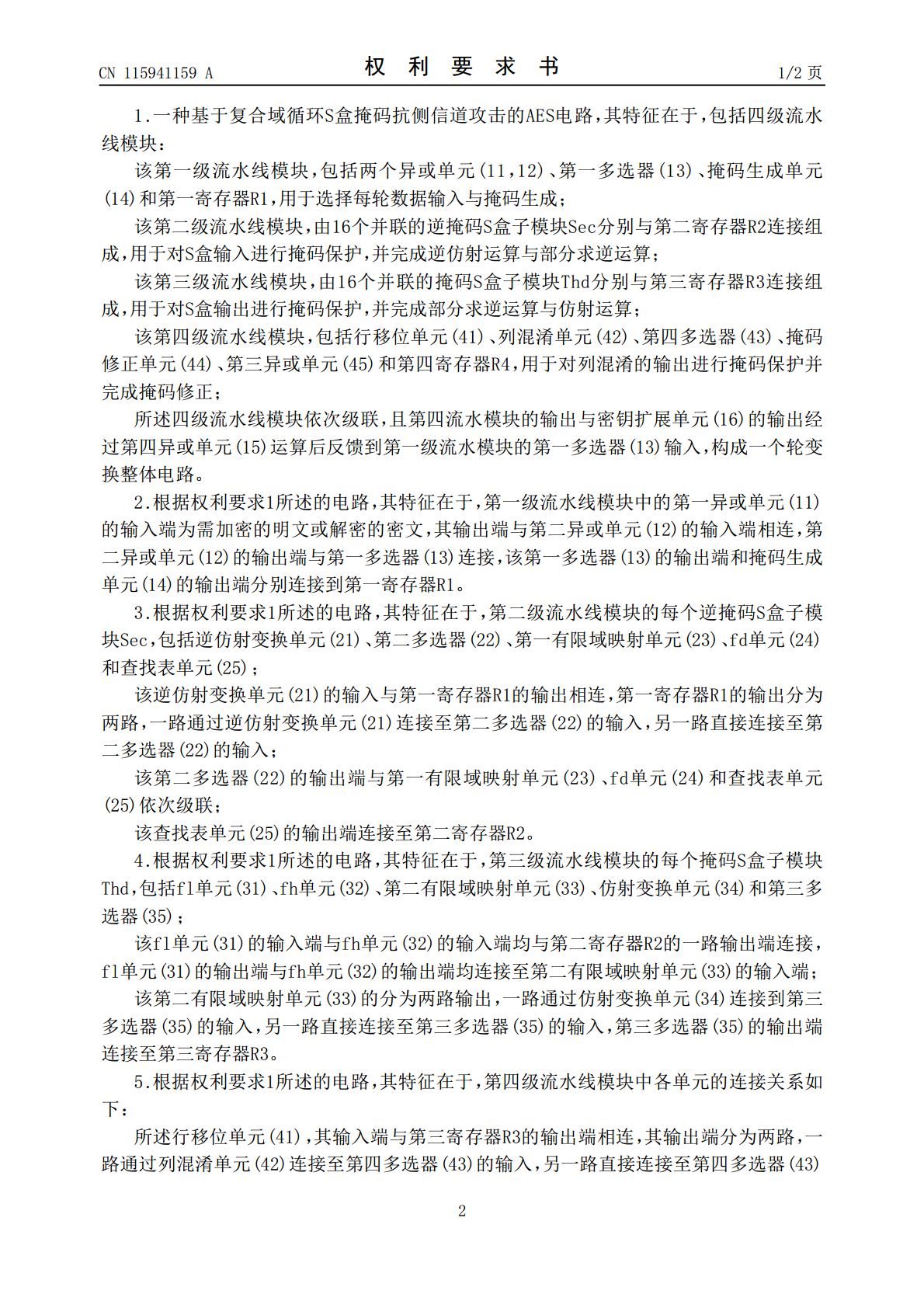

本发明公开了一种基于复合域循环S盒掩码抗侧信道攻击的AES电路,主要解决现有抵抗高阶侧信道攻击时硬件资源消耗大的问题。其由四级流水线模块依次级联构成:第一级模块用于选择每轮数据输入与掩码生成;第二级模块由16个并联的逆掩码S盒子模块分别与第二寄存器组成,实现S盒输入防护、逆仿射运算与部分求逆运算;第三级模块由16个并联的掩码S盒子模块分别与第三寄存器组成,实现S盒输出防护、部分求逆运算与仿射运算;第四级模块实现列混淆输出防护与掩码修正,其输出经过轮密钥加操作后反馈到第一级模块的第一多选器,构成一个轮变换整

基于随机掩码的AES算法抗DPA攻击硬件实现.docx

基于随机掩码的AES算法抗DPA攻击硬件实现基于随机掩码的AES算法抗DPA攻击硬件实现摘要:随着信息技术的快速发展,密码学的安全性显得尤为重要。在各种密码学算法中,对称加密算法中的AES算法是应用广泛的一种算法。然而,本论文重点关注DPA(差分功耗分析)攻击对AES算法的威胁,并提出了一种基于随机掩码的AES算法抗DPA攻击的硬件实现方案。1.引言1.1背景随着信息技术的迅猛发展,数据安全性逐渐成为人们关注的焦点之一。然而,各种密码学算法都存在着一定的漏洞和攻击手段。其中,DPA攻击是一种高效的对称加密

针对AES算法的抗侧信道攻击方法研究的开题报告.docx

针对AES算法的抗侧信道攻击方法研究的开题报告一、研究背景与意义随着信息通信技术的不断发展和应用,保护数据的安全已经成为了至关重要的问题。因此,安全加密算法的研究和应用已经成为了信息安全领域的重要研究方向之一。而AES算法作为一种目前最为流行的对称加密算法,其安全性和效率都得到了广泛的认可。但是在实际应用中,AES算法仍然存在一些安全方面的隐患,其中最为严重的就是侧信道攻击。侧信道攻击是指通过监测设备的电磁、功耗等其他侧信道信息,利用差分功耗分析、差分电磁分析等手段,破解加密算法的一种攻击方式。侧信道攻击

针对AES算法的抗侧信道攻击方法研究的中期报告.docx

针对AES算法的抗侧信道攻击方法研究的中期报告1.研究背景AES算法是一种被广泛应用的对称加密算法,但其存在侧信道攻击的风险。侧信道攻击是一种基于非传统密码学攻击的方法,攻击者通过分析加密过程中产生的电磁辐射、功耗、时间等信息,获取密钥信息。因此,研究针对AES算法的抗侧信道攻击方法具有重大的理论和应用价值。2.研究内容本次研究旨在设计一种有效的抗侧信道攻击的AES算法,并分析其安全性和性能。2.1算法设计本研究采用基于掩盖的对抗侧信道攻击方法,即在加密过程中添加随机掩盖操作,使攻击者无法从侧信道信息中获

S盒抗侧信道攻击能力的分析测评关键技术研究.docx

S盒抗侧信道攻击能力的分析测评关键技术研究标题:S盒抗侧信道攻击能力的分析测评关键技术研究摘要:随着侧信道攻击技术的不断发展,密码算法的安全性受到了极大的挑战。其中,侧信道攻击的重要手段之一为S盒分析,因此研究S盒抗侧信道攻击能力的关键技术成为了一项紧迫而重要的任务。本论文通过对S盒抗侧信道攻击能力进行分析和测评,研究了相关的关键技术,并提出了改进的方法,以提高密码算法的安全性。关键词:S盒,侧信道攻击,抗攻击能力,关键技术,密码算法一、引言近年来,随着物联网的蓬勃发展和计算能力的不断提高,密码算法的安全