基于可重构密码算法的共享平衡算子循环阵列映射方法.pdf

mm****酱吖

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于可重构密码算法的共享平衡算子循环阵列映射方法.pdf

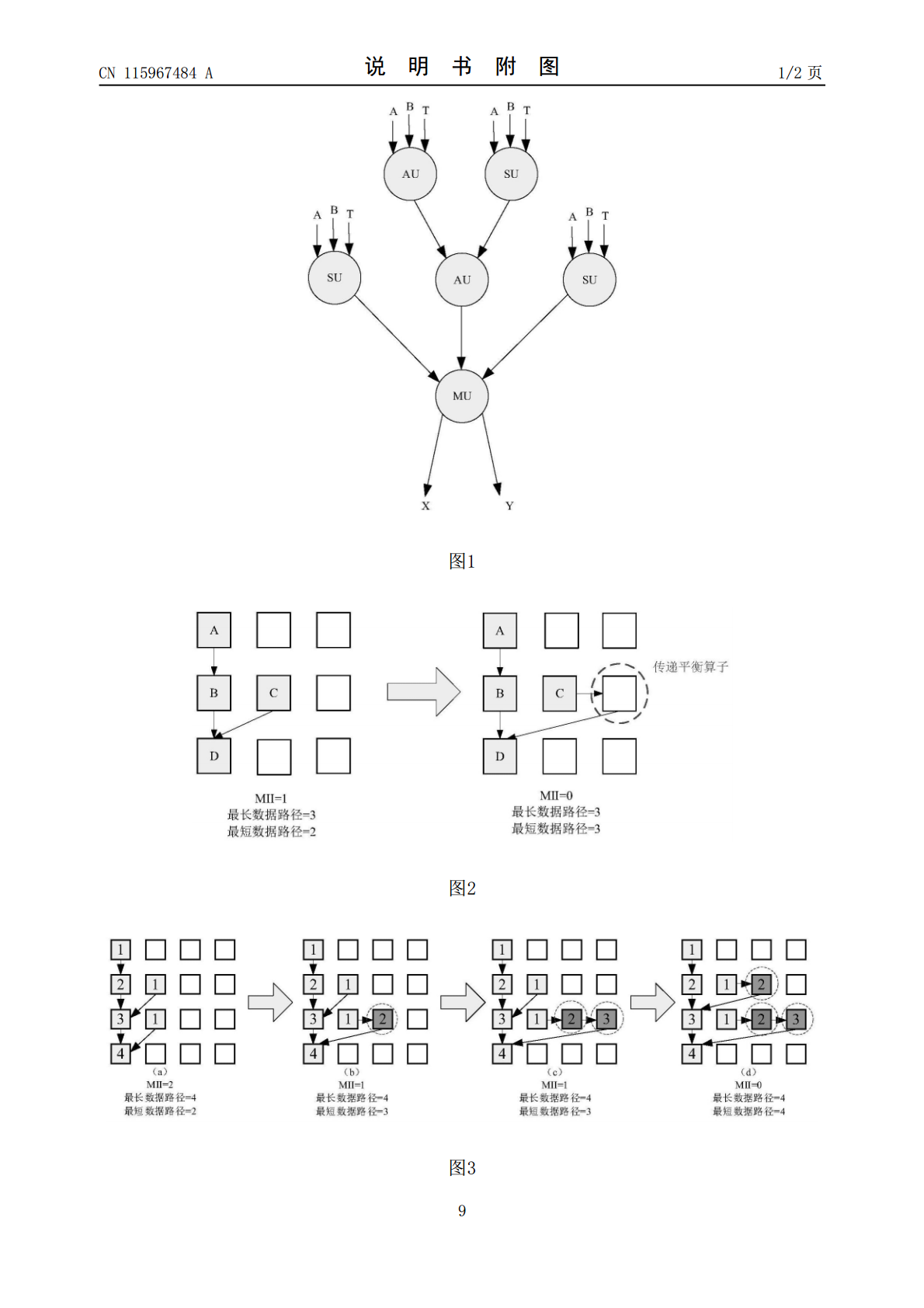

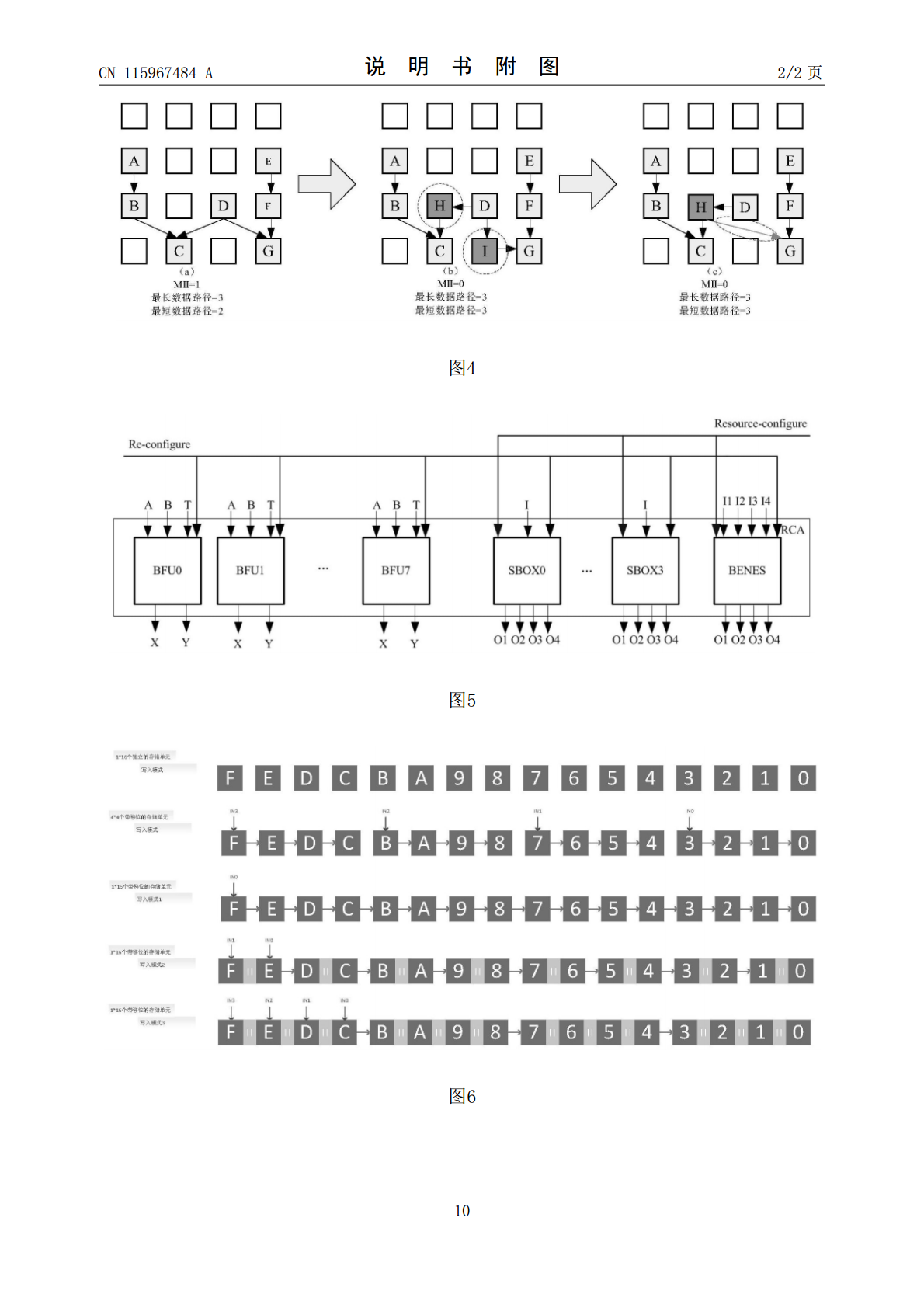

本发明针对循环体内以及多轮循环体间的数据通信进行分析设计,提供了一种基于可重构密码算法的共享平衡算子循环阵列映射方法。本发明采用平衡节点算子方式对映射图进行优化,使其拥有最小的迭代间隔和最大的流水性能,解决了手工配置流水性能差的问题,节约了大量的人力脑力劳动,不需要人工计算手动添加平衡算子节点。本发明采用共享平衡节点算子的方案处理多扇出的算子平衡节点,使得计算资源最小化以及性能最大化。采用存储数据单元SREG进行传递数据通信,解决了循环体间数据的通信占用较多传递算子资源的问题,节约了大量的硬件资源,进一步

基于粗粒度可重构密码阵列的AES算法映射实现.docx

基于粗粒度可重构密码阵列的AES算法映射实现基于粗粒度可重构密码阵列的AES算法映射实现1.引言密钥保护对于信息安全至关重要,特别是在现代信息技术高度发达的时代。高级加密标准(AES)是一种广泛应用的对称密码算法,被广泛用于保护网络通信、数据存储和传输中的敏感信息。然而,由于计算能力的不断发展,传统的软件实现AES算法已经逐渐变得容易受到攻击。为了提高AES算法的安全性和性能,研究人员提出了基于粗粒度可重构密码阵列的AES算法映射实现。本文将从AES算法的背景、粗粒度可重构密码阵列的相关概念、映射实现的方

基于可重构处理器REMUS--Ⅱ的对称密码算法映射与实现的开题报告.docx

基于可重构处理器REMUS--Ⅱ的对称密码算法映射与实现的开题报告一、研究背景随着信息技术的不断发展,数字化信息的安全性问题越来越重要。对称密码算法在信息安全领域扮演着至关重要的角色,其广泛应用于密码学、网络安全、电子商务和数字证书等领域。可重构处理器是一种能够根据不同需求重新配置硬件资源的处理器,其具有灵活性、可扩展性和高性能特点,常用于安全处理器的设计和实现。为提高对称密码算法的安全性和效率,实现对称密码算法的映射和实现成为了目前的研究热点之一。REMUS--Ⅱ是一款基于可重构处理器技术的处理器,其具

基于存储划分和路径重用的粗粒度可重构结构循环映射算法.docx

基于存储划分和路径重用的粗粒度可重构结构循环映射算法随着现代计算机的发展,对计算机内部结构的优化逐渐成为了当今的热点话题之一。其中,循环映射算法作为优化计算机内部循环结构的一种方法,备受研究者们的关注。本文将着重介绍一种基于存储划分和路径重用的粗粒度可重构结构循环映射算法。在初步介绍该算法前,有必要先明确一下循环映射算法所涉及到的一些概念。循环结构即为研究领域中的基本单位,其表示为类似于for循环这样的结构。循环结构常常会出现在程序中的计算密集部分,因此循环映射算法的优化效果直接决定了循环结构的效率。而粗

可重构算子阵列FPGA的结构研究.docx

可重构算子阵列FPGA的结构研究综述随着硬件设计的不断发展,越来越多的应用需要在硬件上实现高效的算法。然而,现有的固定结构的硬件设计往往难以适应应用需求的不断变化,这就要求可重构计算机的出现。可重构计算机采用可重构逻辑单元和可编程连接的结构,提供了一种灵活,高效的硬件设计方法。其中,可重构算子阵列FPGA是一种具有很高学术和工程价值的可编程逻辑器件。本文将对可重构算子阵列FPGA的结构及其研究进行探讨。可重构算子阵列FPGA的概述FPGA是一种可编程逻辑器件,其内部包含大量的可编程逻辑单元和可编程连接资源