一种高线性度采样开关电路.pdf

森林****来了

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种高线性度采样开关电路.pdf

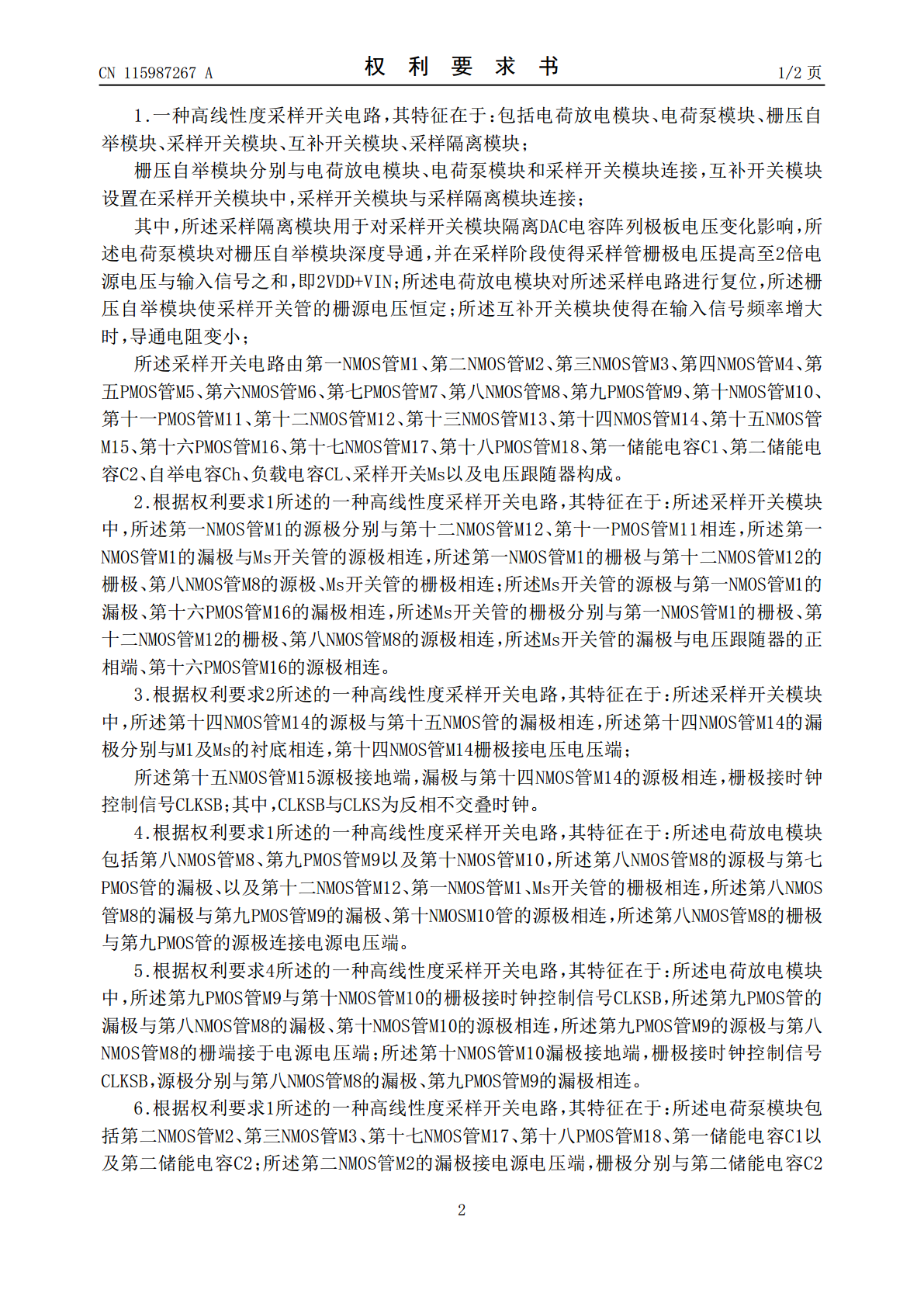

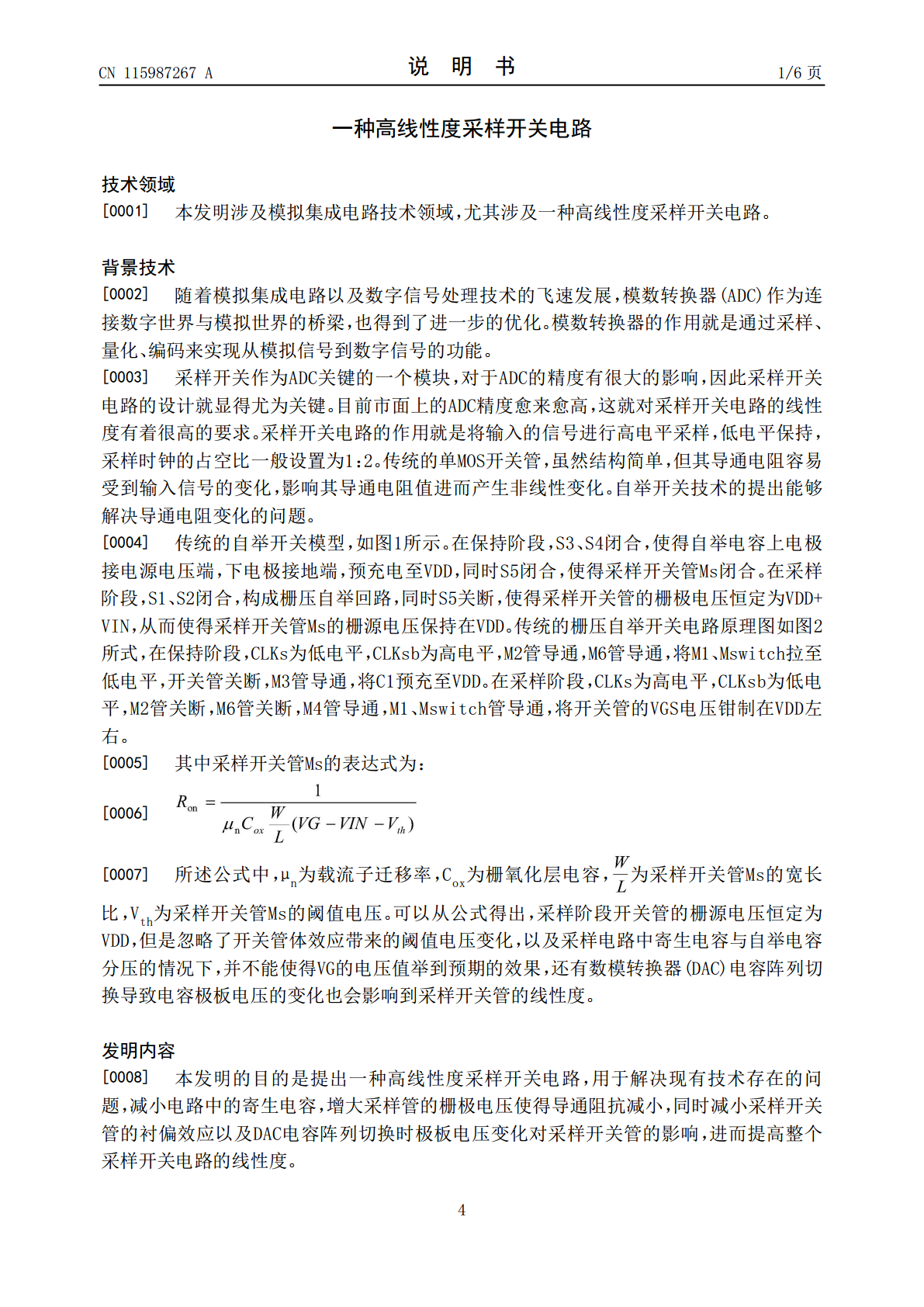

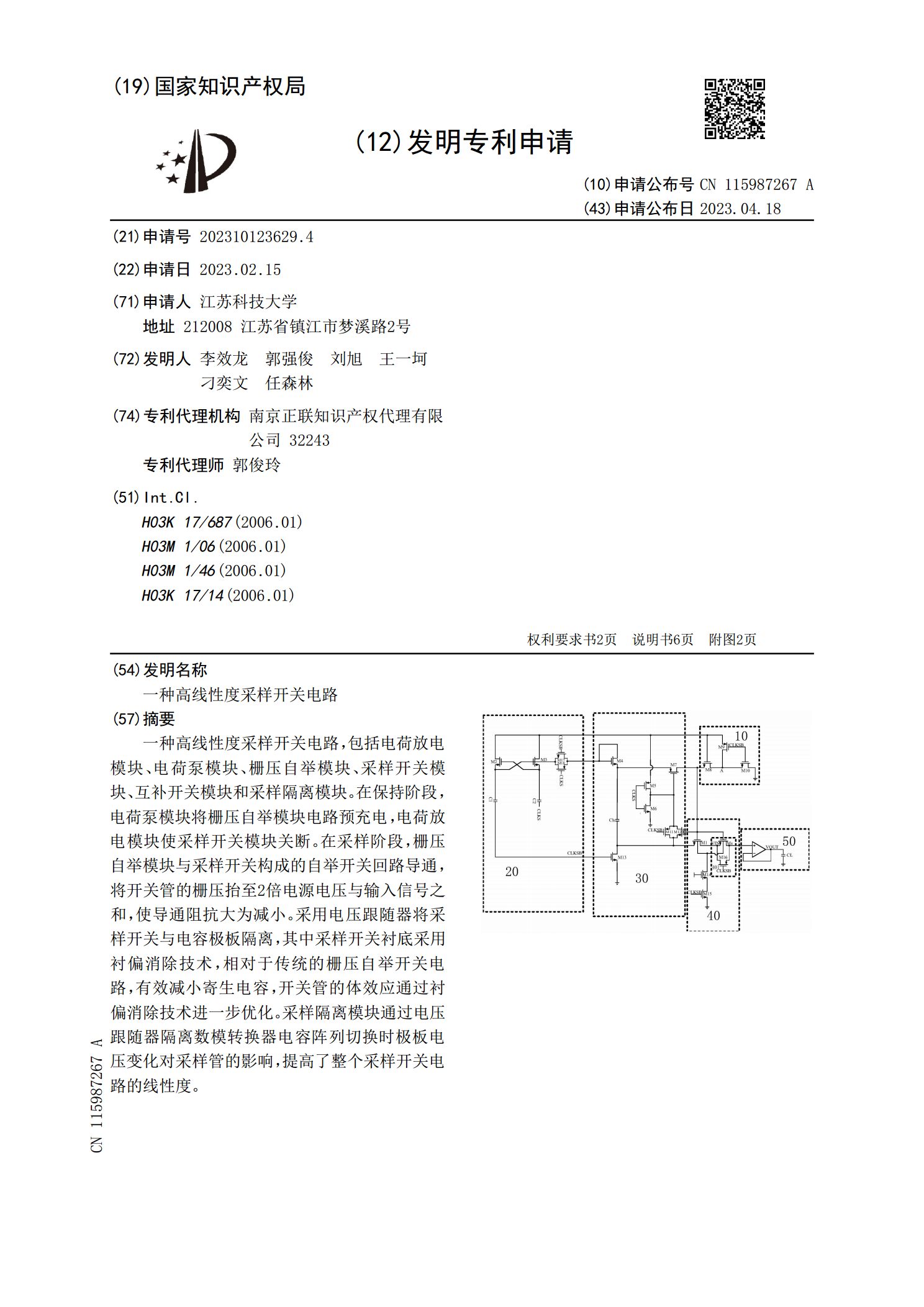

一种高线性度采样开关电路,包括电荷放电模块、电荷泵模块、栅压自举模块、采样开关模块、互补开关模块和采样隔离模块。在保持阶段,电荷泵模块将栅压自举模块电路预充电,电荷放电模块使采样开关模块关断。在采样阶段,栅压自举模块与采样开关构成的自举开关回路导通,将开关管的栅压抬至2倍电源电压与输入信号之和,使导通阻抗大为减小。采用电压跟随器将采样开关与电容极板隔离,其中采样开关衬底采用衬偏消除技术,相对于传统的栅压自举开关电路,有效减小寄生电容,开关管的体效应通过衬偏消除技术进一步优化。采样隔离模块通过电压跟随器隔离

一种高线性度梯度线圈设计方法.pdf

本发明公开了一种高线性度梯度线圈设计方法,提出了两个新的傅里叶级数展开的电流密度函数,引入流函数;选定N个目标区域内的离散目标点,依据毕奥‑萨伐尔定律推导目标场点的磁场表达式,与电流密度函数之间构建关系矩阵;通过设定目标场点的取值,选取流函数的最小曲率作为约束线圈的罚函数,设定罚函数的约束因子,通过正则化方法求解电流密度表达式中的待定系数,得到圆柱表面的电流密度分布情况;使用流函数对电流密度进行离散,生成线圈的绕组图。本发明通过改进目标场法设计梯度线圈,极大的提高了梯度场的线性度;并且在计算前预先设定了圆

一种高线性度sigma-delta调制器.pdf

本申请公开一种高线性度sigma‑delta调制器,包括:积分器、加法器、多bit量化器、反馈DAC;所述加法器与所述积分器、多bit量化器、反馈DAC之间串联连接;所述加法器包括两级:第一级为有源加法器,第二级为无源放大器,所述有源加法器的输出端与所述无源放大器的输入端电性连接。本发明采用两级加法器结构,有源加法器仅提供原来1/2的增益,在有源加法器之后通过引入无源放大的电荷泵进行无源2倍的放大,在总增益未改变的同时,降低了加法器中的运算放大器的输出范围,从而提高了调制器的线性度,使得有源运算放大器的输

一种高线性度多比特相位插值器.pdf

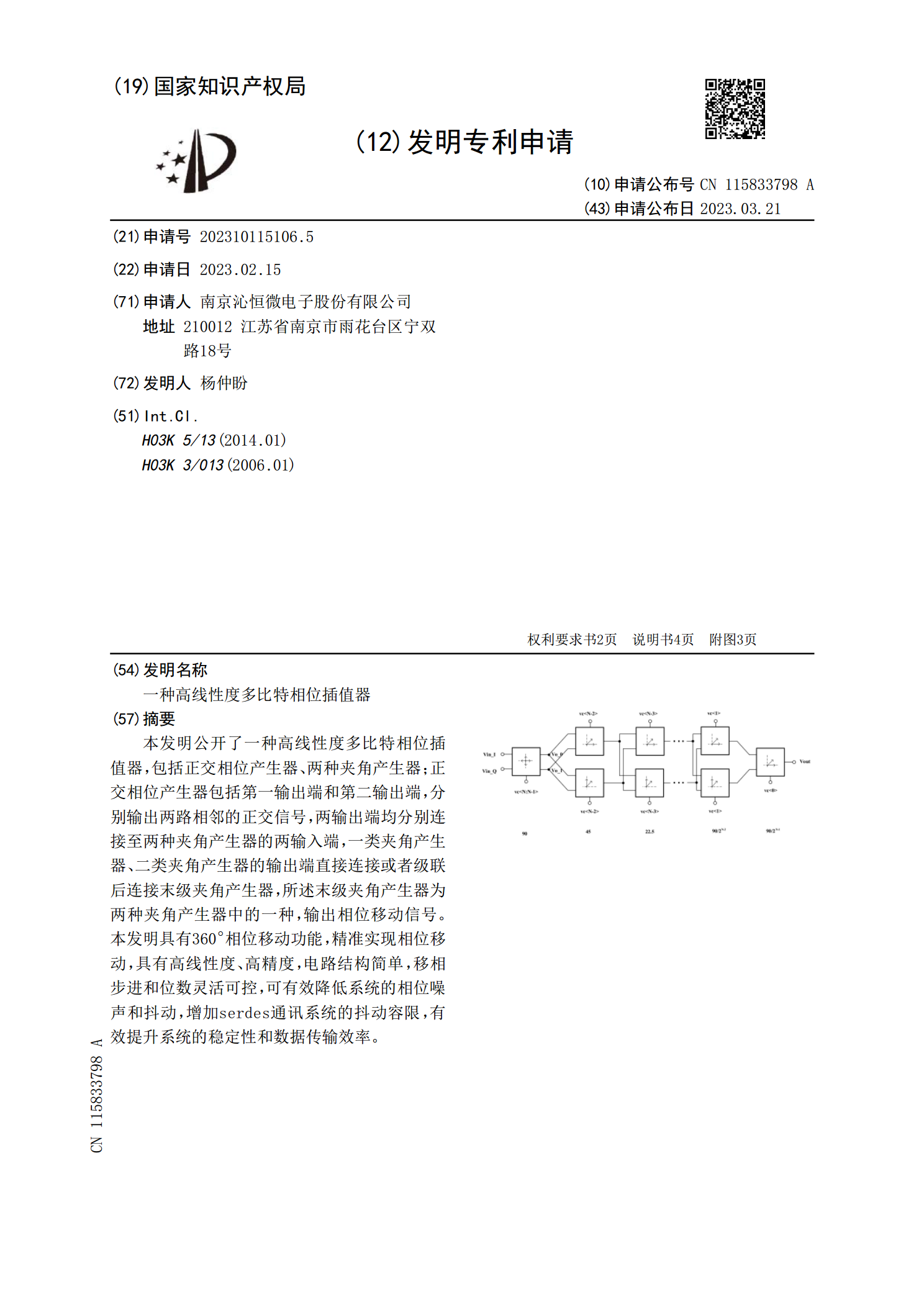

本发明公开了一种高线性度多比特相位插值器,包括正交相位产生器、两种夹角产生器;正交相位产生器包括第一输出端和第二输出端,分别输出两路相邻的正交信号,两输出端均分别连接至两种夹角产生器的两输入端,一类夹角产生器、二类夹角产生器的输出端直接连接或者级联后连接末级夹角产生器,所述末级夹角产生器为两种夹角产生器中的一种,输出相位移动信号。本发明具有360°相位移动功能,精准实现相位移动,具有高线性度、高精度,电路结构简单,移相步进和位数灵活可控,可有效降低系统的相位噪声和抖动,增加serdes通讯系统的抖动容限,

低插入损耗高隔离度SOI射频开关电路的研究.docx

低插入损耗高隔离度SOI射频开关电路的研究IntroductionAsthedemandforhigh-performanceradiofrequency(RF)switchcircuitscontinuestogrow,researchershaveincreasinglyfocusedontheuseofsilicon-on-insulator(SOI)technologyasapromisingplatformforRFswitchdesign.SOItechnologyprovidessevera