数据包的处理方法和设备.pdf

是你****盟主

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

数据包的处理方法和设备.pdf

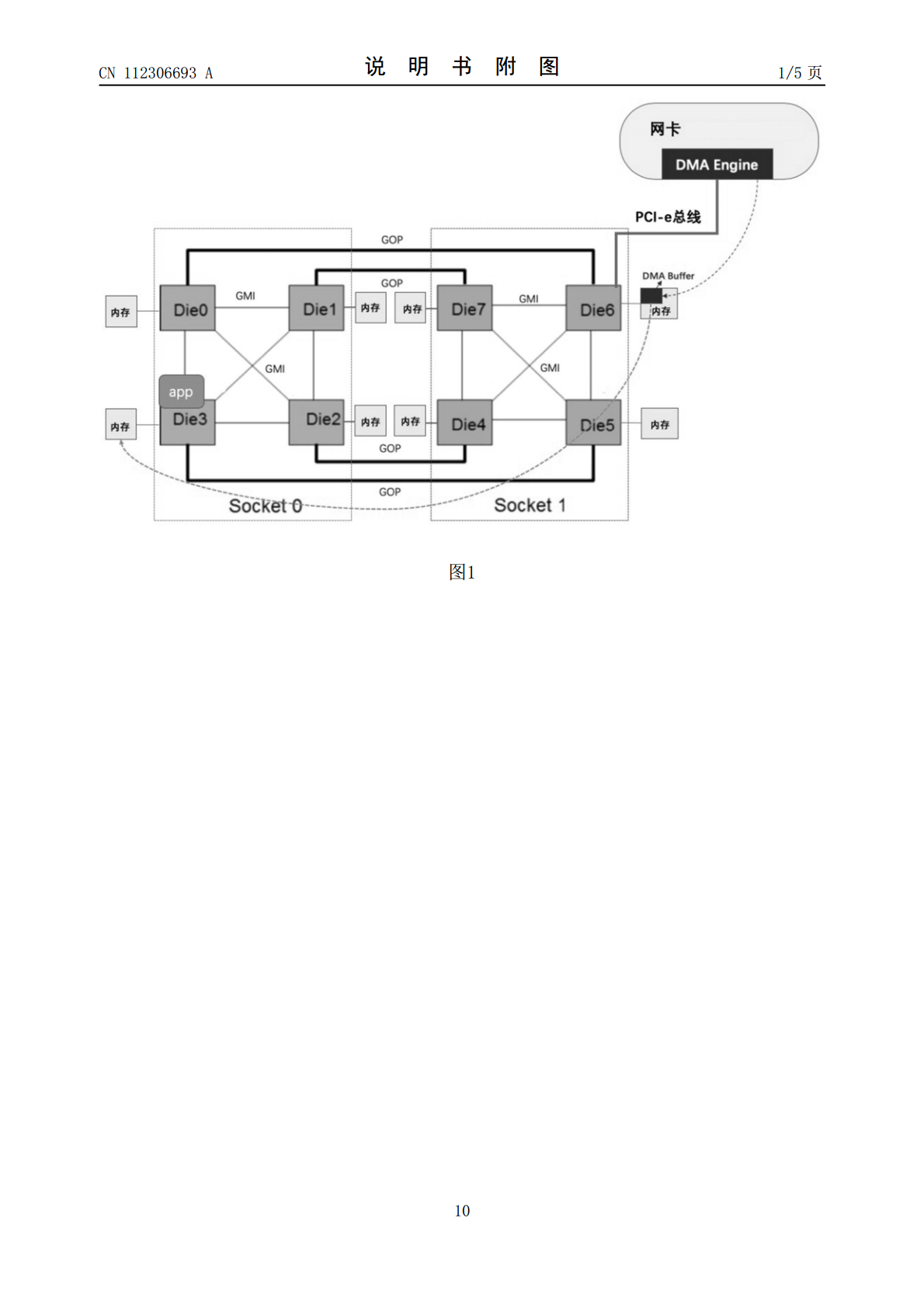

本说明书实施例提出了一种数据包的处理方法和设备,其中,上述数据包的处理方法中,网卡接收到数据包之后,对上述数据包进行解析,获得上述数据包对应的数据流标识,然后,网卡根据上述数据流标识将上述数据包放入网卡队列,进而网卡从上述网卡队列中获取数据包,将获取的数据包发送到上述网卡队列对应的DMA内存,并产生相应中断,这样,与上述DMA内存所在的内存节点连接的目标CPU节点,就可以响应上述中断,从本地DMA内存中读取数据包,并对读取的数据包进行处理,这时,中断和DMA内存在同一个Die上,降低了跨Die存取数据的时

数据包处理方法和相关设备.pdf

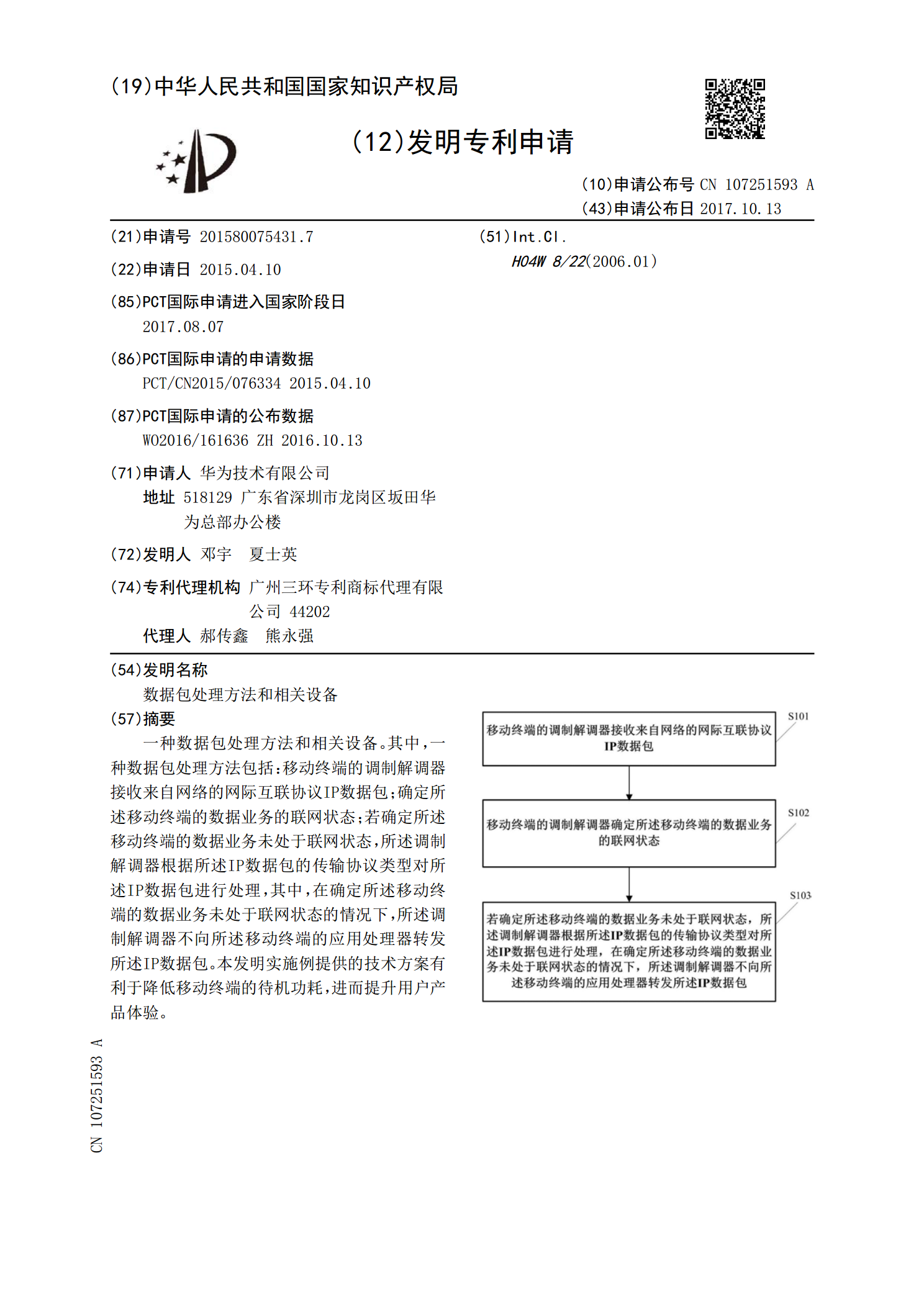

一种数据包处理方法和相关设备。其中,一种数据包处理方法包括:移动终端的调制解调器接收来自网络的网际互联协议IP数据包;确定所述移动终端的数据业务的联网状态;若确定所述移动终端的数据业务未处于联网状态,所述调制解调器根据所述IP数据包的传输协议类型对所述IP数据包进行处理,其中,在确定所述移动终端的数据业务未处于联网状态的情况下,所述调制解调器不向所述移动终端的应用处理器转发所述IP数据包。本发明实施例提供的技术方案有利于降低移动终端的待机功耗,进而提升用户产品体验。

用于智能设备的数据包处理方法和系统.pdf

本发明实施例提供一种用于智能设备的DNS数据包处理方法和系统,其中,方法包括:在通过智能设备内核层的数据包中,对DNS数据包进行捕获;对所述捕获的DNS数据包进行数据处理,并丢弃所述捕获的DNS数据包;将处理后的DNS数据包发送至所述DNS数据包的目的端口。本发明通过在数据包经过内核时对其进行捕获和处理,改变了现有技术中数据包在应用层处理需要经过两次内存拷贝,处理效率不高的状况,实现了DNS数据包的更高效处理,进一步地,由于处理效率更高,也能增强系统的抗D‑dos攻击的能力。

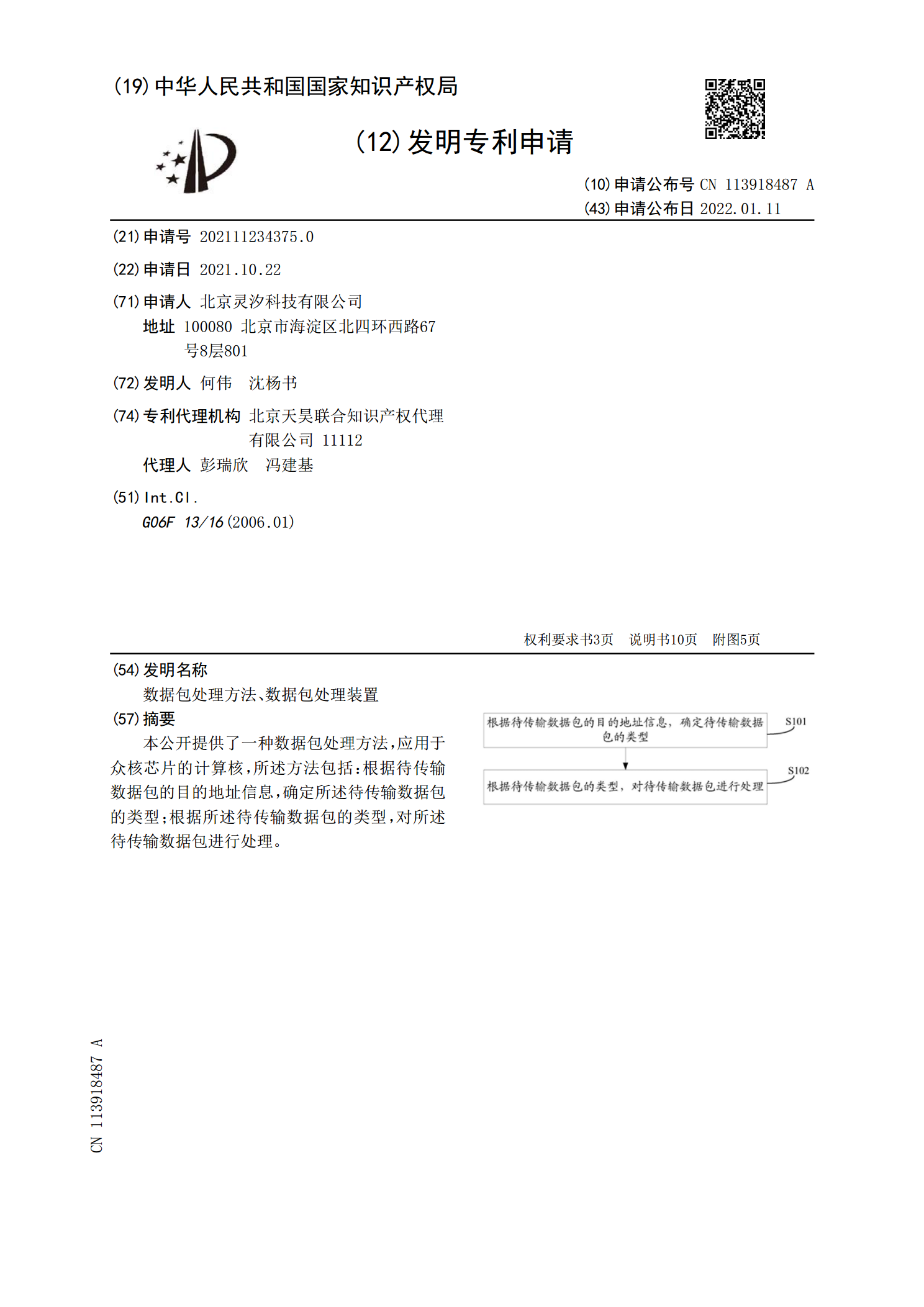

数据包处理方法、数据包处理装置.pdf

本公开提供了一种数据包处理方法,应用于众核芯片的计算核,所述方法包括:根据待传输数据包的目的地址信息,确定所述待传输数据包的类型;根据所述待传输数据包的类型,对所述待传输数据包进行处理。

一种数据包的处理方法和设备.pdf

本发明公开了一种数据包的处理方法和设备,该方法包括:PDCP实体获得待发送给FPGA芯片的发送数据包,在发送数据包中添加发送序列号,将携带所述发送序列号的发送数据包发送给FPGA芯片;FPGA芯片利用发送序列号得到携带接收序列号的接收数据包;PDCP实体接收来自FPGA芯片的携带接收序列号的接收数据包,将接收数据包缓存到接收队列,利用接收数据包中携带的接收序列号对接收队列内缓存的接收数据包进行重新排列;PDCP实体按照接收队列内的重新排列的接收数据包,将接收队列内的接收数据包发送给RLC实体。本发明实施例