(完整word版)实验四-八位七段数码管动态显示电路的设计.doc

睿德****找我

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

(完整word版)实验四-八位七段数码管动态显示电路的设计.doc

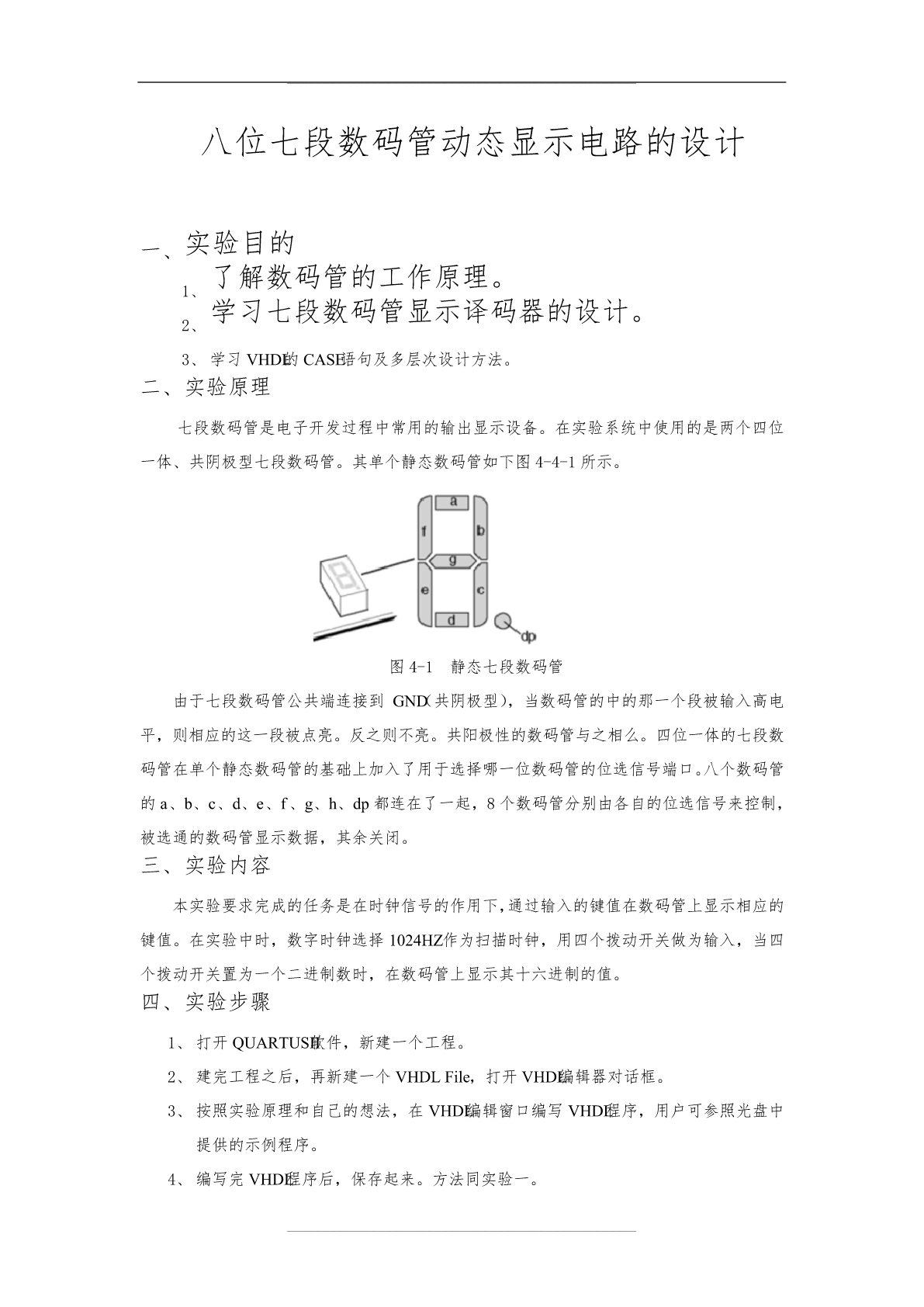

八位七段数码管动态显示电路的设计实验目的了解数码管的工作原理。学习七段数码管显示译码器的设计。学习VHDL的CASE语句及多层次设计方法。实验原理七段数码管是电子开发过程中常用的输出显示设备。在实验系统中使用的是两个四位一体、共阴极型七段数码管。其单个静态数码管如下图4-4-1所示。图4-1静态七段数码管由于七段数码管公共端连接到GND(共阴极型),当数码管的中的那一个段被输入高电平,则相应的这一段被点亮。反之则不亮。共阳极性的数码管与之相么。四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一

(完整word版)实验四-八位七段数码管动态显示电路的设计.doc

八位七段数码管动态显示电路的设计实验目的了解数码管的工作原理。学习七段数码管显示译码器的设计。学习VHDL的CASE语句及多层次设计方法。实验原理七段数码管是电子开发过程中常用的输出显示设备。在实验系统中使用的是两个四位一体、共阴极型七段数码管。其单个静态数码管如下图4-4-1所示。图4-1静态七段数码管由于七段数码管公共端连接到GND(共阴极型),当数码管的中的那一个段被输入高电平,则相应的这一段被点亮。反之则不亮。共阳极性的数码管与之相么。四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一

实验四-八位七段数码管动态显示电路的设计.pdf

__________________________________________________八位七段数码管动态显示电路的设计一、实验目的了解数码管的工作原理。1、学习七段数码管显示译码器的设计。2、3、学习VHDL的CASE语句及多层次设计方法。二、实验原理七段数码管是电子开发过程中常用的输出显示设备。在实验系统中使用的是两个四位一体、共阴极型七段数码管。其单个静态数码管如下图4-4-1所示。图4-1静态七段数码管由于七段数码管公共端连接到GND(共阴极型),当数码管的中的那一个段被输入高电平,则

八位七段数码管动态显示电路设计.doc

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。七段显示器的脚位和线路图如下图4.1所示(其第一支接脚位于俯视图之左上角)。图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时

八位七段数码管动态显示电路设计.doc

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。七段显示器的脚位和线路图如下图4.1所示(其第一支接脚位于俯视图之左上角)。图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。因此,七段显示器依其