USB-SATA及PCIE接口.doc

慧红****ad

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

PCIe接口和接口系统.pdf

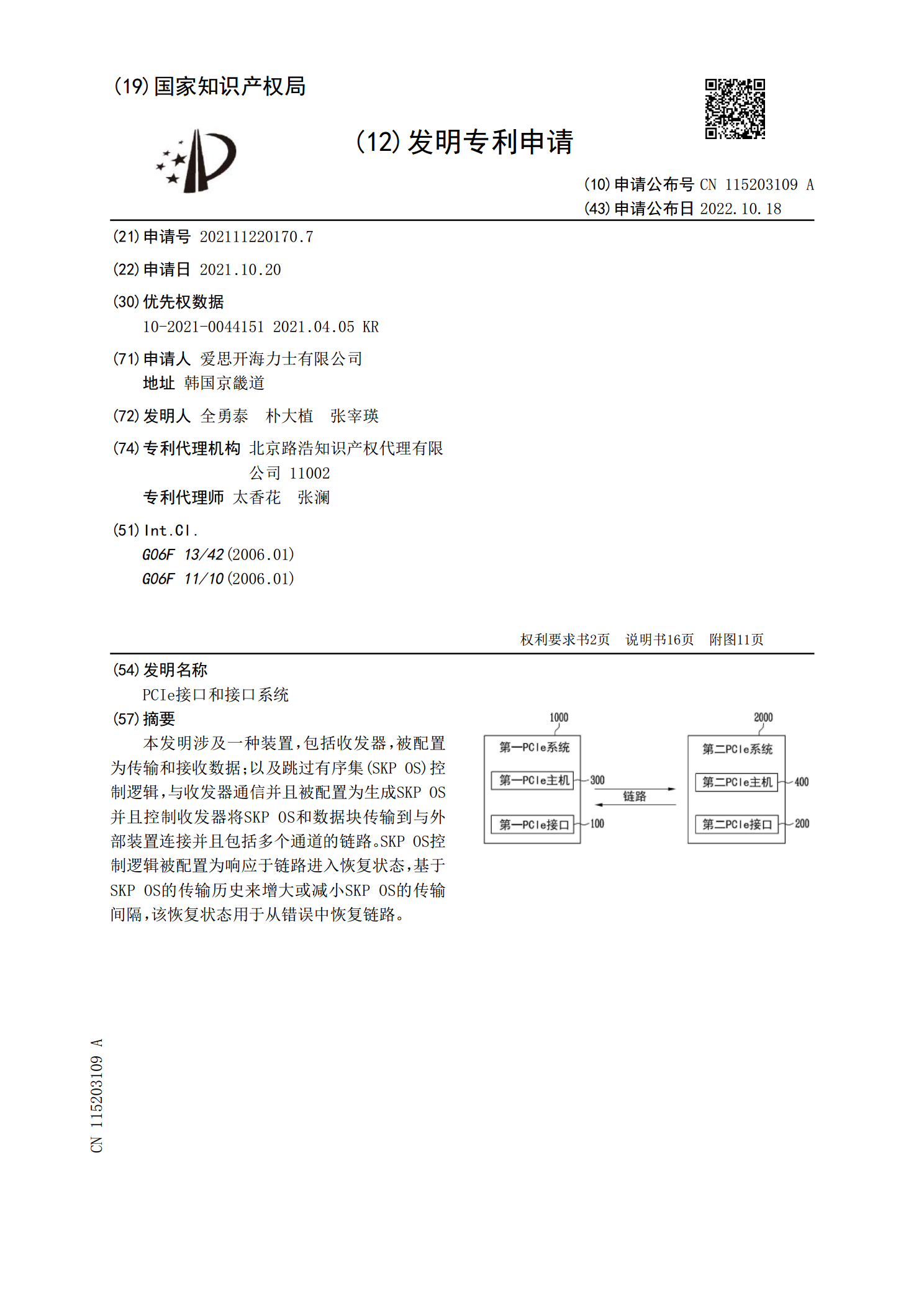

本发明涉及一种装置,包括收发器,被配置为传输和接收数据;以及跳过有序集(SKPOS)控制逻辑,与收发器通信并且被配置为生成SKPOS并且控制收发器将SKPOS和数据块传输到与外部装置连接并且包括多个通道的链路。SKPOS控制逻辑被配置为响应于链路进入恢复状态,基于SKPOS的传输历史来增大或减小SKPOS的传输间隔,该恢复状态用于从错误中恢复链路。

USB-SATA及PCIE接口.doc

USB,SATA及PCIE接口USB,SATA及PCIE接口USB,SATA及PCIE接口1.USB(UniversalSerialBus)USB1.0USB1。0是在1996年出现的,速度只有1。5Mb/s(位每秒);1998年升级为USB1.1,速度也大大提升到12Mb/s。USB2。0USB2.0规范是由USB1。1规范演变而来,它的最大理论传输速率达到了480Mbps,折算为MB为60MB/s,足以满足大多数外设的速率要求。USB2。0中的“增强主机控制器接口"(EHCI)定义了一个与USB1。1

USB-SATA及PCIE接口.doc

USB,SATA及PCIE接口USB,SATA及PCIE接口USB,SATA及PCIE接口1.USB(UniversalSerialBus)USB1.0USB1。0是在1996年出现的,速度只有1。5Mb/s(位每秒);1998年升级为USB1.1,速度也大大提升到12Mb/s。USB2。0USB2.0规范是由USB1。1规范演变而来,它的最大理论传输速率达到了480Mbps,折算为MB为60MB/s,足以满足大多数外设的速率要求。USB2。0中的“增强主机控制器接口"(EHCI)定义了一个与USB1。1

基于PCIe接口的DMA传输方法.pdf

本发明公开了一种基于PCIe接口的DMA传输方法,检测主机下发的DMA读指令信息,根据所述DMA读指令信息生成存储器读请求包,为每个存储器读请求包请求到的数据分配在SRAM缓存地址、DDR缓存地址、SRAM读取地址、预留写SRAM起始位置信息并且从CPLD额外信息RAM的A端口写入;接收主机响应的带数据的完成包并且提取其中的TAG字段,以所述提取到的TAG字段作为地址,从CPLD额外信息RAM的B端口读取之前写入的SRAM缓存地址、DDR缓存地址、SRAM读取地址、预留写SRAM起始位置信息,以所述SRA

xilinx-PCIE2.0接口-EP端设计总结.doc

PCIE说明PCIE协议定义了多种设备:根复合体(RootComplex),交换器(Switch),端点(Endpoingt),断就(Port),PCIE到PCI/PCI-X的桥(Bridge)等。根复合体是将CPU和主存储器连接到PCIE线路结构上的设备,能带包CPI启动PCIE事务和访问主存储器;交换器可以将任务由一个端口路由到另一个端口,在系统中用于多设备的互联,具体的路由方法包括ID路由,地址路由,隐含路由;Endpoint是指一个世纪的设备(请求者或完成者);port是设备与链路的接口;Brid