ARINC429总线收发器芯片DEI1016的原理及应用.docx

宏硕****mo

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

ARINC429总线收发器芯片DEI1016的原理及应用.docx

ARINC429总线收发器芯片DEI1016的原理及应用摘要:简要介绍了DeviceEngineering公司的DEI1016芯片的功能,详细说明了利用DEI1016芯片实现ARINC429协议数据通讯系统的设计方法,给出了比较具体的电路设计及软件解决方法。关键词:ARINC429;差分输出;FIFO;可编程器件1概述目前,ARINC429收发器主要以DeviceEngineering公司的DEI1016及BD429来配套使用。其中DEI1016提供有标准航空串行数据和16bit宽数据总线接口。该接口电路

多通道ARINC429总线收发器设计与实现的综述报告.docx

多通道ARINC429总线收发器设计与实现的综述报告ARINC429是一种常见的数字数据通信协议。它通常在航空、航天、军事等应用中被广泛使用。ARINC429提供了一种可靠的、高效的数据传输方案,支持多个设备之间进行通信,并具有高度的实时性和可扩展性。多通道ARINC429总线收发器是一种允许多个收发器共享同一总线的设备。本文将介绍多通道ARINC429总线收发器的设计和实现。多通道ARINC429总线收发器的设计需要考虑以下几个方面:信号传输、信号过滤和接口电路。首先,信号传输方面主要包括ARINC42

多通道ARINC429总线收发器设计与实现的开题报告.docx

多通道ARINC429总线收发器设计与实现的开题报告一、选题背景ARINC429总线是航空电子设备间相互通信的标准总线,广泛应用于飞机上的各种航电设备中。由于其稳定可靠、传输速率高等优点,ARINC429总线已成为了国际航空电子领域中的标准总线之一。因此,ARINC429总线收发器的设计与实现具有重要的实际意义和研究价值。二、研究内容本课题拟设计一种基于FPGA的ARINC429总线多通道收发器,主要包括以下内容:1.研究ARINC429总线协议及相关标准,深入理解ARINC429总线在航空电子设备中的应

包含收发器与控制器的CAN总线节点芯片.pdf

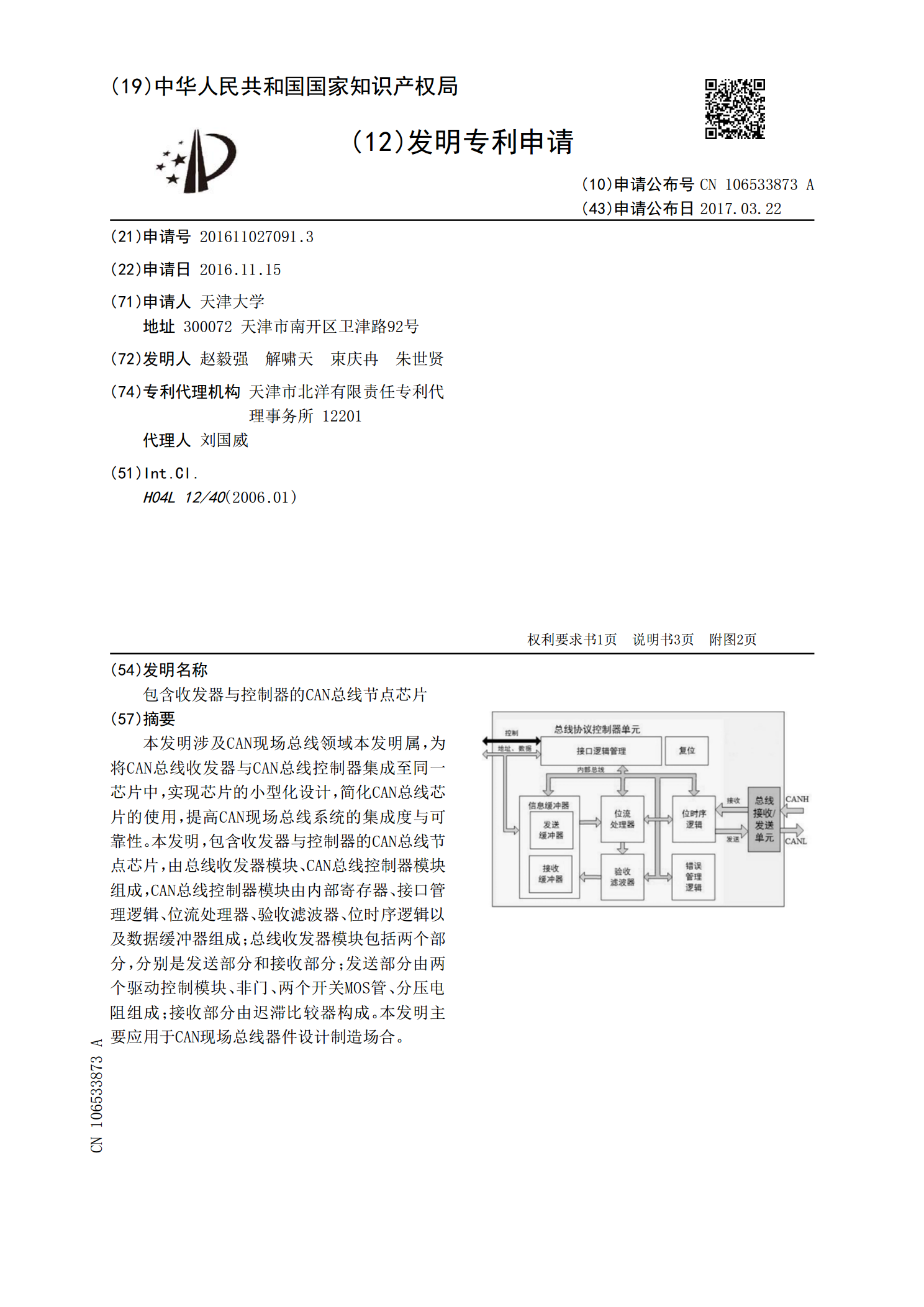

本发明涉及CAN现场总线领域本发明属,为将CAN总线收发器与CAN总线控制器集成至同一芯片中,实现芯片的小型化设计,简化CAN总线芯片的使用,提高CAN现场总线系统的集成度与可靠性。本发明,包含收发器与控制器的CAN总线节点芯片,由总线收发器模块、CAN总线控制器模块组成,CAN总线控制器模块由内部寄存器、接口管理逻辑、位流处理器、验收滤波器、位时序逻辑以及数据缓冲器组成;总线收发器模块包括两个部分,分别是发送部分和接收部分;发送部分由两个驱动控制模块、非门、两个开关MOS管、分压电阻组成;接收部分由迟滞

总线收发器.pdf

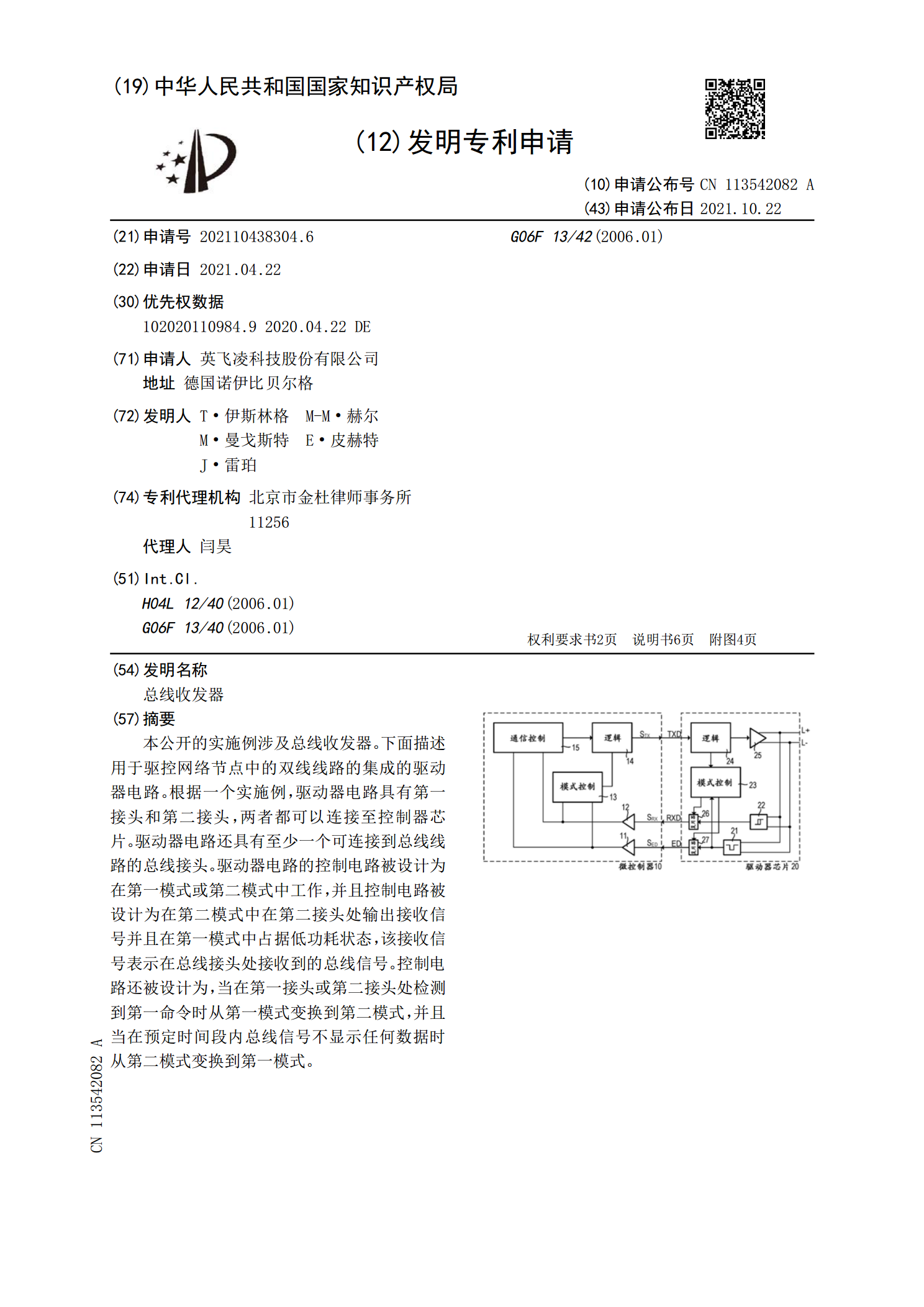

本公开的实施例涉及总线收发器。下面描述用于驱控网络节点中的双线线路的集成的驱动器电路。根据一个实施例,驱动器电路具有第一接头和第二接头,两者都可以连接至控制器芯片。驱动器电路还具有至少一个可连接到总线线路的总线接头。驱动器电路的控制电路被设计为在第一模式或第二模式中工作,并且控制电路被设计为在第二模式中在第二接头处输出接收信号并且在第一模式中占据低功耗状态,该接收信号表示在总线接头处接收到的总线信号。控制电路还被设计为,当在第一接头或第二接头处检测到第一命令时从第一模式变换到第二模式,并且当在预定时间段内