微处理器以及相关储存方法.pdf

书生****萌哒

亲,该文档总共26页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

微处理器以及相关储存方法.pdf

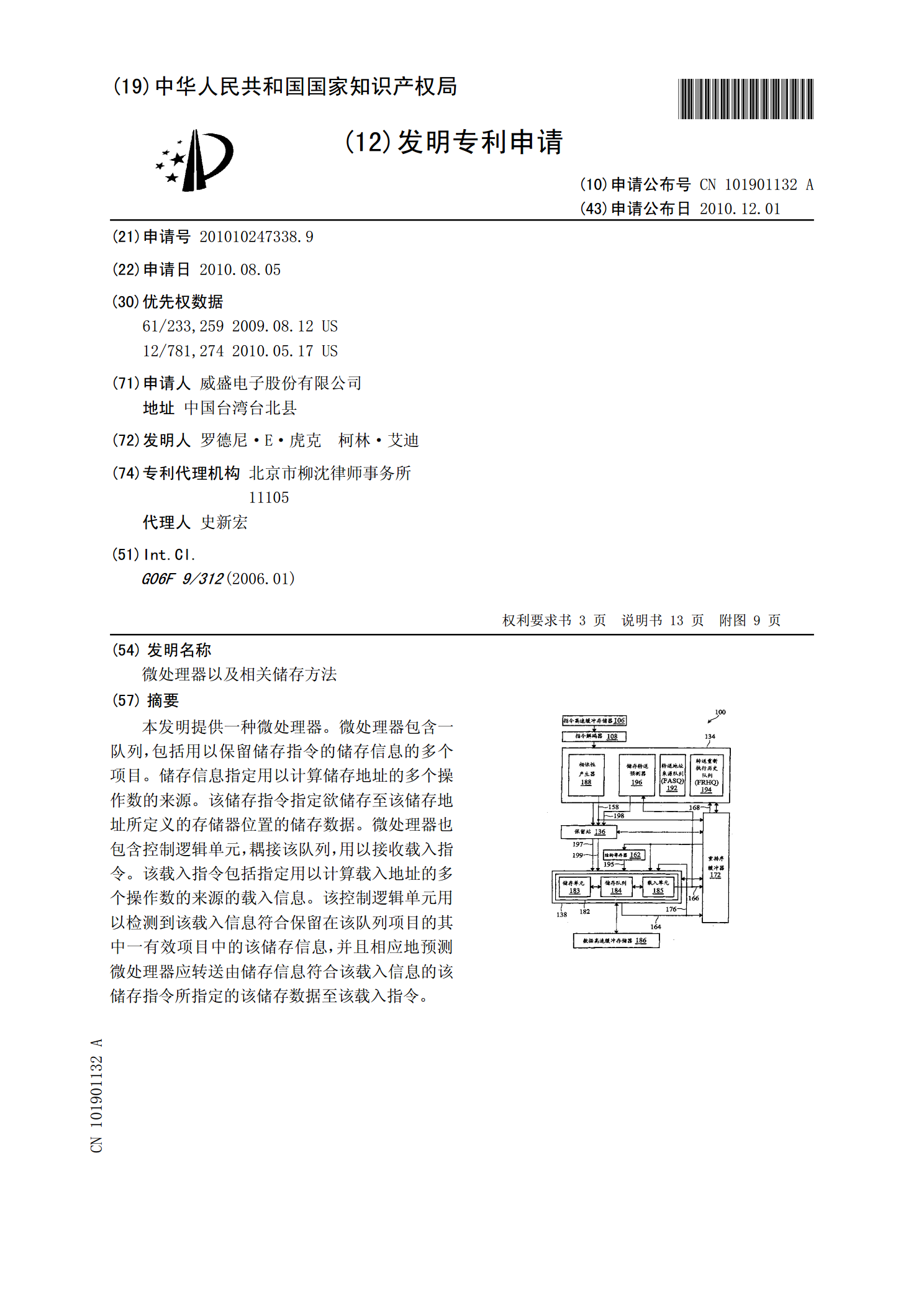

本发明提供一种微处理器。微处理器包含一队列,包括用以保留储存指令的储存信息的多个项目。储存信息指定用以计算储存地址的多个操作数的来源。该储存指令指定欲储存至该储存地址所定义的存储器位置的储存数据。微处理器也包含控制逻辑单元,耦接该队列,用以接收载入指令。该载入指令包括指定用以计算载入地址的多个操作数的来源的载入信息。该控制逻辑单元用以检测到该载入信息符合保留在该队列项目的其中一有效项目中的该储存信息,并且相应地预测微处理器应转送由储存信息符合该载入信息的该储存指令所指定的该储存数据至该载入指令。

数据储存装置以及其操作方法.pdf

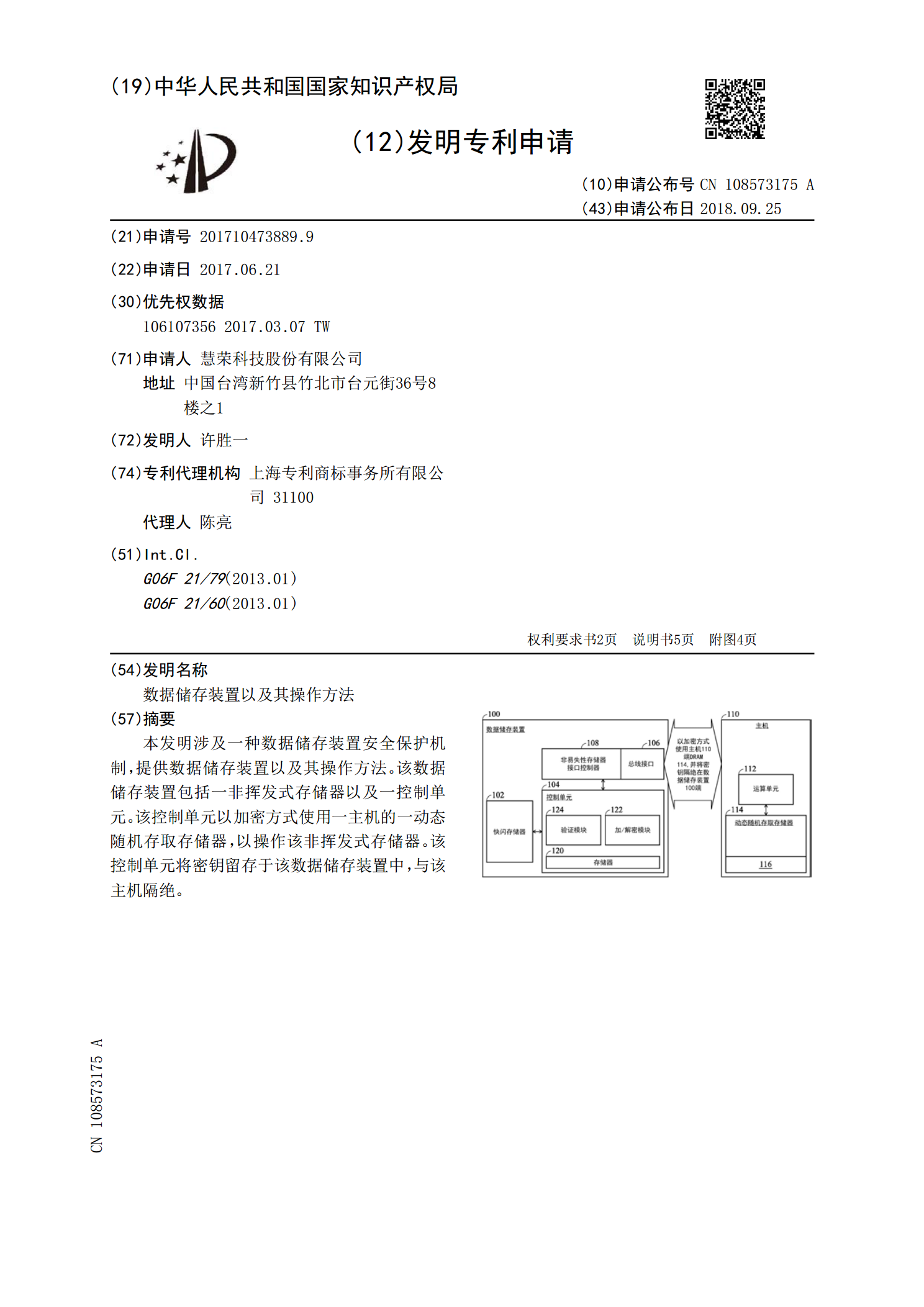

本发明涉及一种数据储存装置安全保护机制,提供数据储存装置以及其操作方法。该数据储存装置包括一非挥发式存储器以及一控制单元。该控制单元以加密方式使用一主机的一动态随机存取存储器,以操作该非挥发式存储器。该控制单元将密钥留存于该数据储存装置中,与该主机隔绝。

数据储存装置以及其操作方法.pdf

本发明涉及数据储存装置以及其操作方法。混和型数据储存装置,除了提供一非挥发性存储器,还规划其中一挥发性存储器提供一特定使用暂存区,分担该非挥发性存储器的存储工作,使写入该特定使用暂存区的数据更存留于该特定使用暂存区,以回应读取要求。

数据权限控制方法、系统、终端以及储存介质.pdf

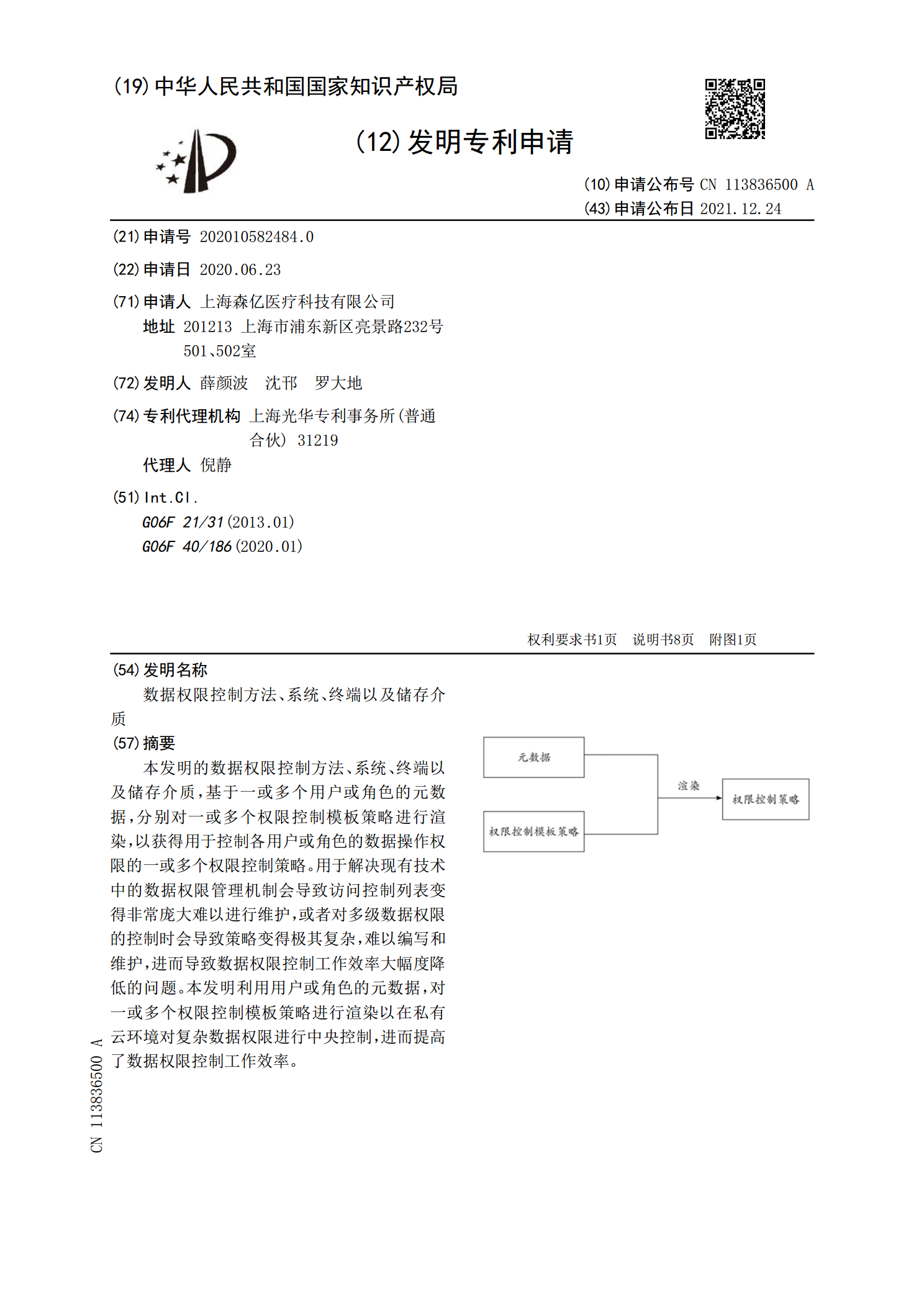

本发明的数据权限控制方法、系统、终端以及储存介质,基于一或多个用户或角色的元数据,分别对一或多个权限控制模板策略进行渲染,以获得用于控制各用户或角色的数据操作权限的一或多个权限控制策略。用于解决现有技术中的数据权限管理机制会导致访问控制列表变得非常庞大难以进行维护,或者对多级数据权限的控制时会导致策略变得极其复杂,难以编写和维护,进而导致数据权限控制工作效率大幅度降低的问题。本发明利用用户或角色的元数据,对一或多个权限控制模板策略进行渲染以在私有云环境对复杂数据权限进行中央控制,进而提高了数据权限控制工作

数据储存系统与其相关方法.pdf

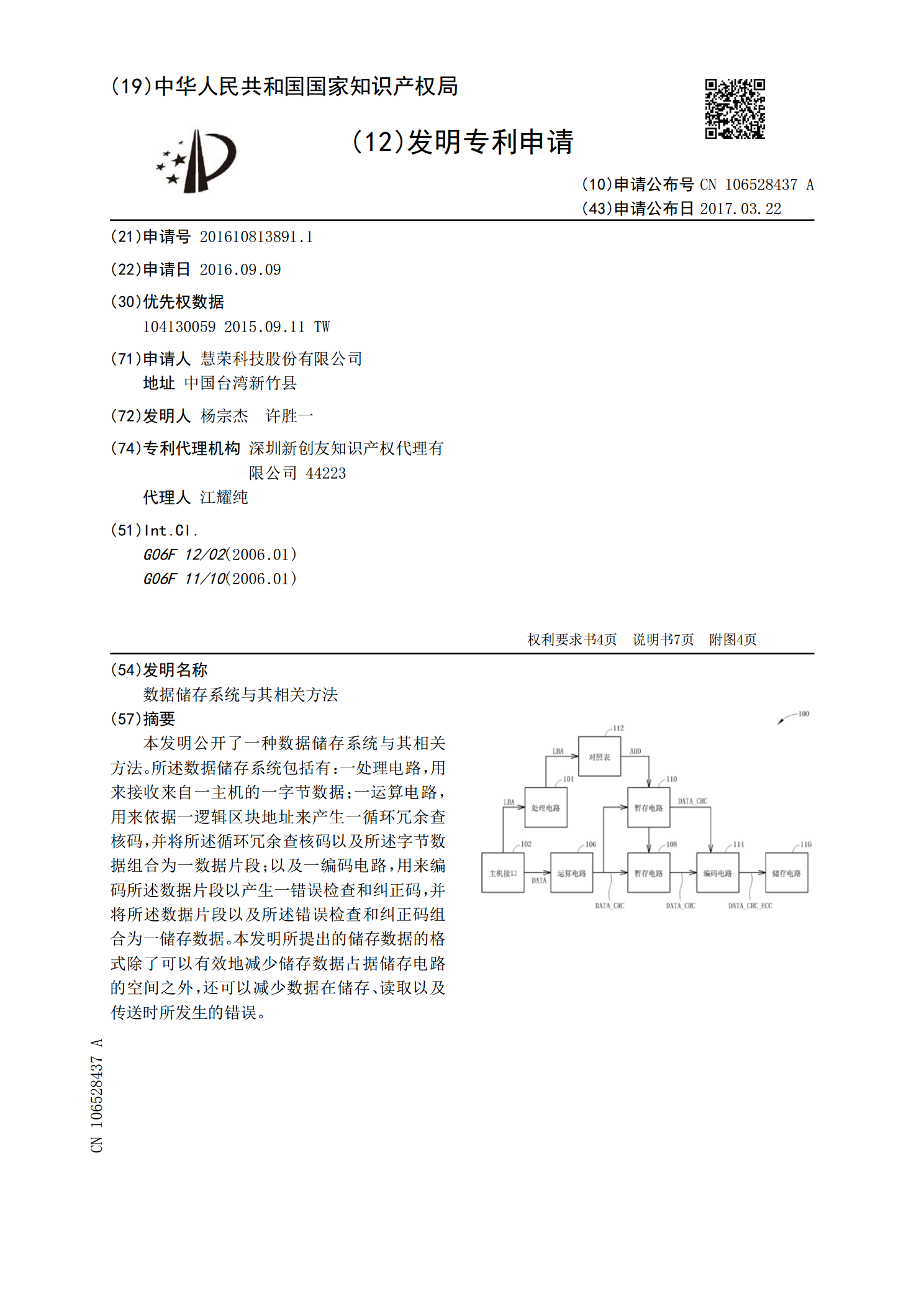

本发明公开了一种数据储存系统与其相关方法。所述数据储存系统包括有:一处理电路,用来接收来自一主机的一字节数据;一运算电路,用来依据一逻辑区块地址来产生一循环冗余查核码,并将所述循环冗余查核码以及所述字节数据组合为一数据片段;以及一编码电路,用来编码所述数据片段以产生一错误检查和纠正码,并将所述数据片段以及所述错误检查和纠正码组合为一储存数据。本发明所提出的储存数据的格式除了可以有效地减少储存数据占据储存电路的空间之外,还可以减少数据在储存、读取以及传送时所发生的错误。