亚阈值低功耗SRAM关键技术研究的中期报告.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

亚阈值低功耗SRAM关键技术研究的中期报告.docx

亚阈值低功耗SRAM关键技术研究的中期报告本研究旨在探讨亚阈值低功耗静态随机存储器(SRAM)的关键技术,中期报告主要包括以下几个方面的研究内容:一、亚阈值低功耗SRAM的简介亚阈值低功耗SRAM是一种新型的存储器技术,其特点是工作电压低、功耗小,可用于低功耗的移动设备、物联网设备等。该类型的SRAM的工作电压通常低于传统SRAM的阈值电压,因此需要特殊的固有延迟补偿技术。二、亚阈值低功耗SRAM的原理及关键技术亚阈值低功耗SRAM的工作原理是基于维持放电器(maintaincell)的工作过程,其中维持

低功耗SRAM存储单元关键技术研究及电路设计的综述报告.docx

低功耗SRAM存储单元关键技术研究及电路设计的综述报告随着移动智能终端设备的普及和互联网的飞速发展,人们对于计算设备和数据传输速率的要求越来越高,而低功耗SRAM存储单元正是研究和开发的焦点,以满足这一需求。随着技术的不断进步,晶体管的尺寸越来越小,从而使得电子器件的功耗得以进一步降低。这些技术的发展和创新为低功耗SRAM存储单元带来了更为广阔的发展前景。低功耗SRAM存储单元的技术瓶颈在于如何将稳定性、容量、速度和功耗之间的平衡发挥到极致,以达到更高效的性能和更持久的可靠性。在低功耗SRAM存储单元的关

1Mb高速低功耗SRAM的设计的中期报告.docx

1Mb高速低功耗SRAM的设计的中期报告本文介绍的是一份1Mb高速低功耗SRAM的中期报告,该项目的目标是设计一个集成电路,以实现高速低功耗的1MbSRAM存储器。1.设计细节在设计过程中,我们首先选择了合适的SRAM单元,然后使用VerilogHDL建立了整个存储器的RTL代码(RegisterTransferLevel)。接下来,我们将SRAM数组分成了1024个块,每个块包含1024个SRAM单元,每个单元有4位数据宽度和1位地址宽度。然后,我们实现了读写逻辑以及基于写入控制的写回机制。此外,我们还

一种亚阈值SRAM读写辅助电路.pdf

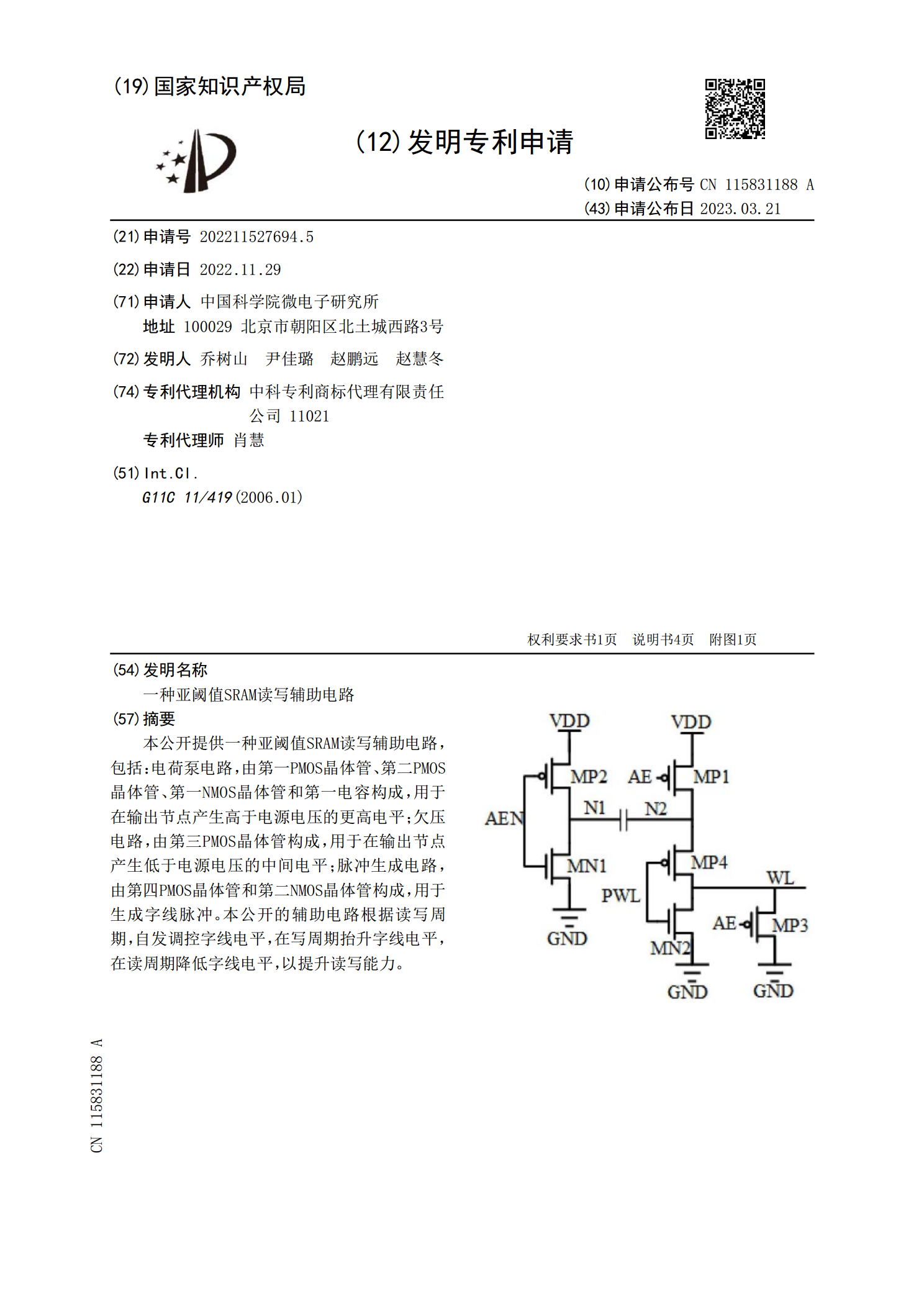

本公开提供一种亚阈值SRAM读写辅助电路,包括:电荷泵电路,由第一PMOS晶体管、第二PMOS晶体管、第一NMOS晶体管和第一电容构成,用于在输出节点产生高于电源电压的更高电平;欠压电路,由第三PMOS晶体管构成,用于在输出节点产生低于电源电压的中间电平;脉冲生成电路,由第四PMOS晶体管和第二NMOS晶体管构成,用于生成字线脉冲。本公开的辅助电路根据读写周期,自发调控字线电平,在写周期抬升字线电平,在读周期降低字线电平,以提升读写能力。

低功耗频率合成器的关键技术研究的中期报告.docx

低功耗频率合成器的关键技术研究的中期报告低功耗频率合成器是一种常用的电路,它可以将一个基准频率合成出高精度的输出频率。在现代电子设备中,低功耗频率合成器被广泛应用于无线通信、数字信号处理、数据转换和控制系统中,因此其功耗和性能的优化一直是研究的热点之一。本研究的目标是设计一种低功耗、高性能的频率合成器,并研究其中的关键技术。本中期报告主要介绍了研究的进展情况,涉及到的内容包括:架构设计、频率分析、器件选择和电路实现等方面。首先,我们结合所研究的应用场景,选择了分数-N架构的频率合成器。该架构具有低功耗、高