一种嵌入式处理器的分支预测器.pdf

fu****级甜

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种嵌入式处理器的分支预测器.pdf

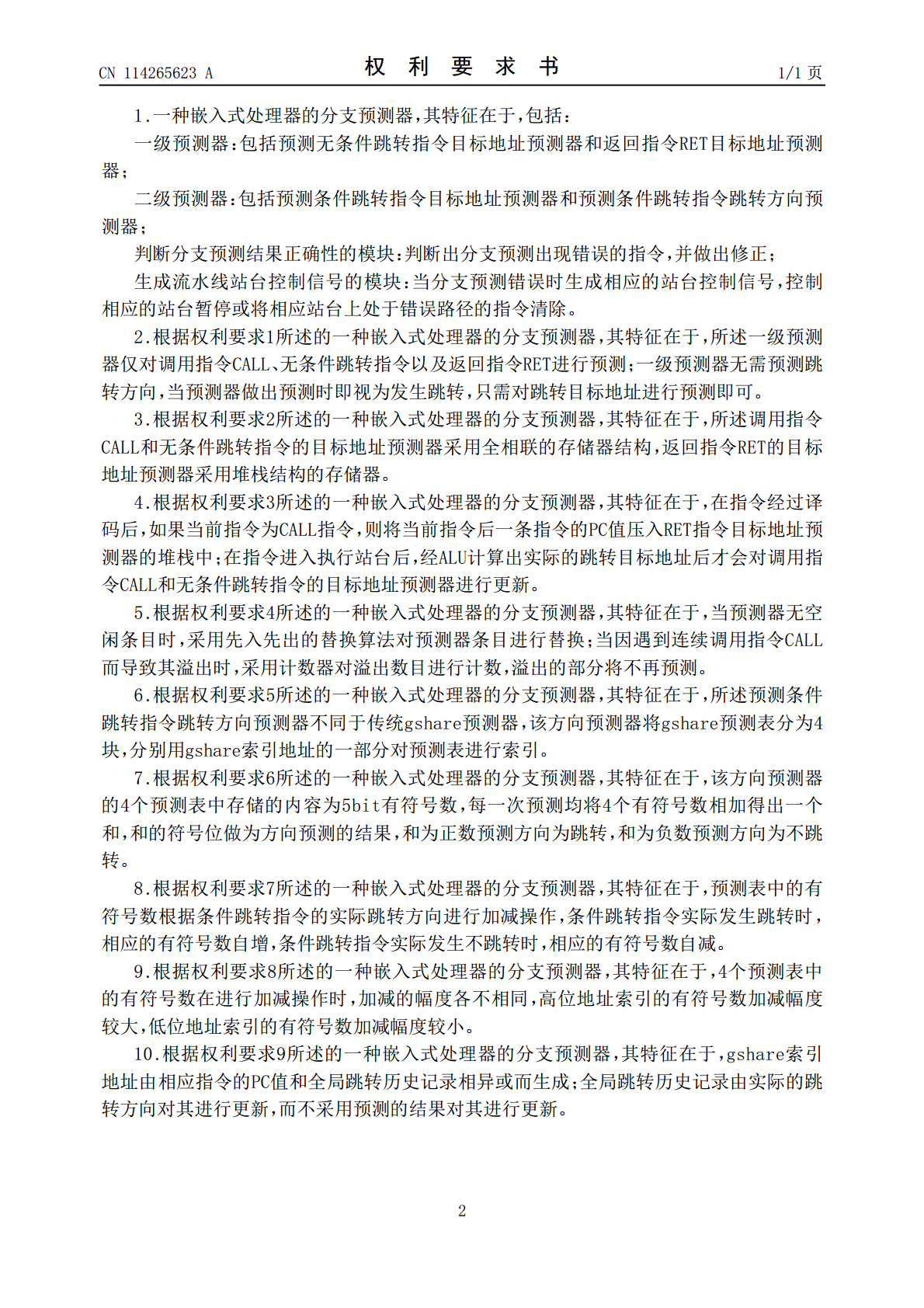

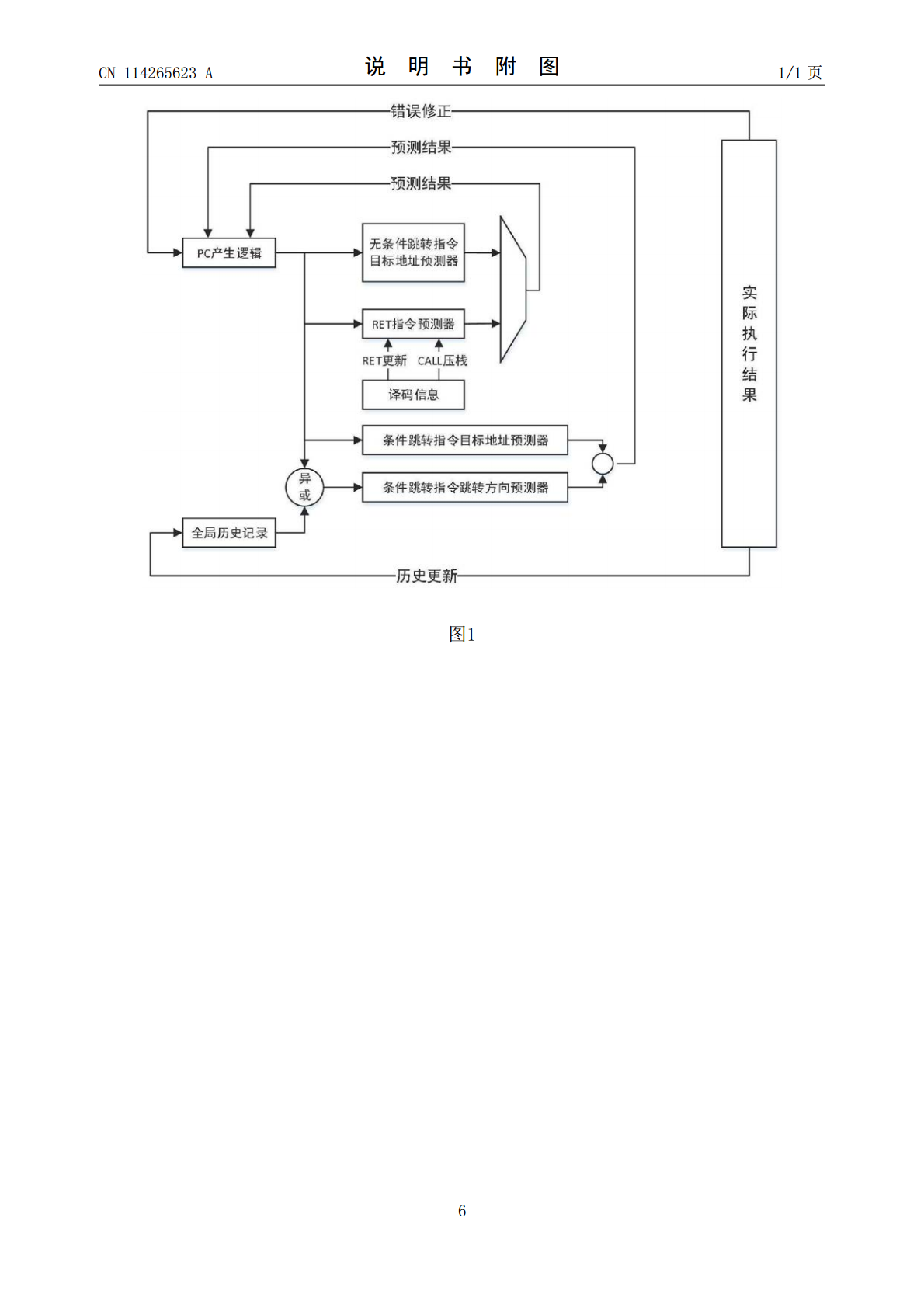

本发明涉及嵌入式处理器技术领域,具体涉及一种嵌入式处理器的分支预测器;包括:一级预测器:包括预测无条件跳转指令目标地址预测器和返回指令RET目标地址预测器;二级预测器:包括预测条件跳转指令目标地址预测器和预测条件跳转指令跳转方向预测器;判断分支预测结果正确性的模块:判断出分支预测出现错误的指令,并做出修正;生成流水线站台控制信号的模块:当分支预测错误时生成相应的站台控制信号,控制相应的站台暂停或将相应站台上处于错误路径的指令清除;该预测器较一级预测器可提供更高的预测准确率。二级预测的方向预测器提供相当预测

分支指令的处理方法、分支预测器及处理器.pdf

本申请实施例提供了一种分支指令的处理方法、分支预测器及处理器,在预测是否对目标分支指令执行跳转操作时,先根据目标分支指令的部分地址,在分支预测表中查找目标分支指令对应的目标分支条目;若在分支预测表中查找到目标分支条目,由于该目标分支条目包括第一字段,且第一字段用于指示M个预测信息,M个预测信息根据目标分支指令的历史跳转信息及影响所述目标分支指令的预测结果的信息预测得到的,M为大于或者等于2的整数,这样就可以根据多个目标分支指令的历史跳转信息及影响目标分支指令的预测结果的信息,共同预测是否对所述目标分支指令

乱序处理器分支预测器性能建模的开题报告.docx

乱序处理器分支预测器性能建模的开题报告一、选题背景随着计算机性能的提高,处理器的管道结构也逐渐变得复杂起来。在这样的复杂结构下,指令的乱序执行也成为现代处理器中常见的执行方式之一。在乱序执行的过程中,还需要考虑指令的依赖关系,以确保在执行指令时,不会出现数据冲突和控制冲突等问题。而为了更好地处理指令之间的依赖关系,在处理器中加入分支预测器是非常重要的。因此,乱序处理器分支预测器的性能建模成为了一项非常重要的任务。二、选题意义分支预测器在乱序处理器中扮演着至关重要的角色。优秀的分支预测器可以提高程序执行的效

基于全局历史分类的间接分支预测器及预测方法.pdf

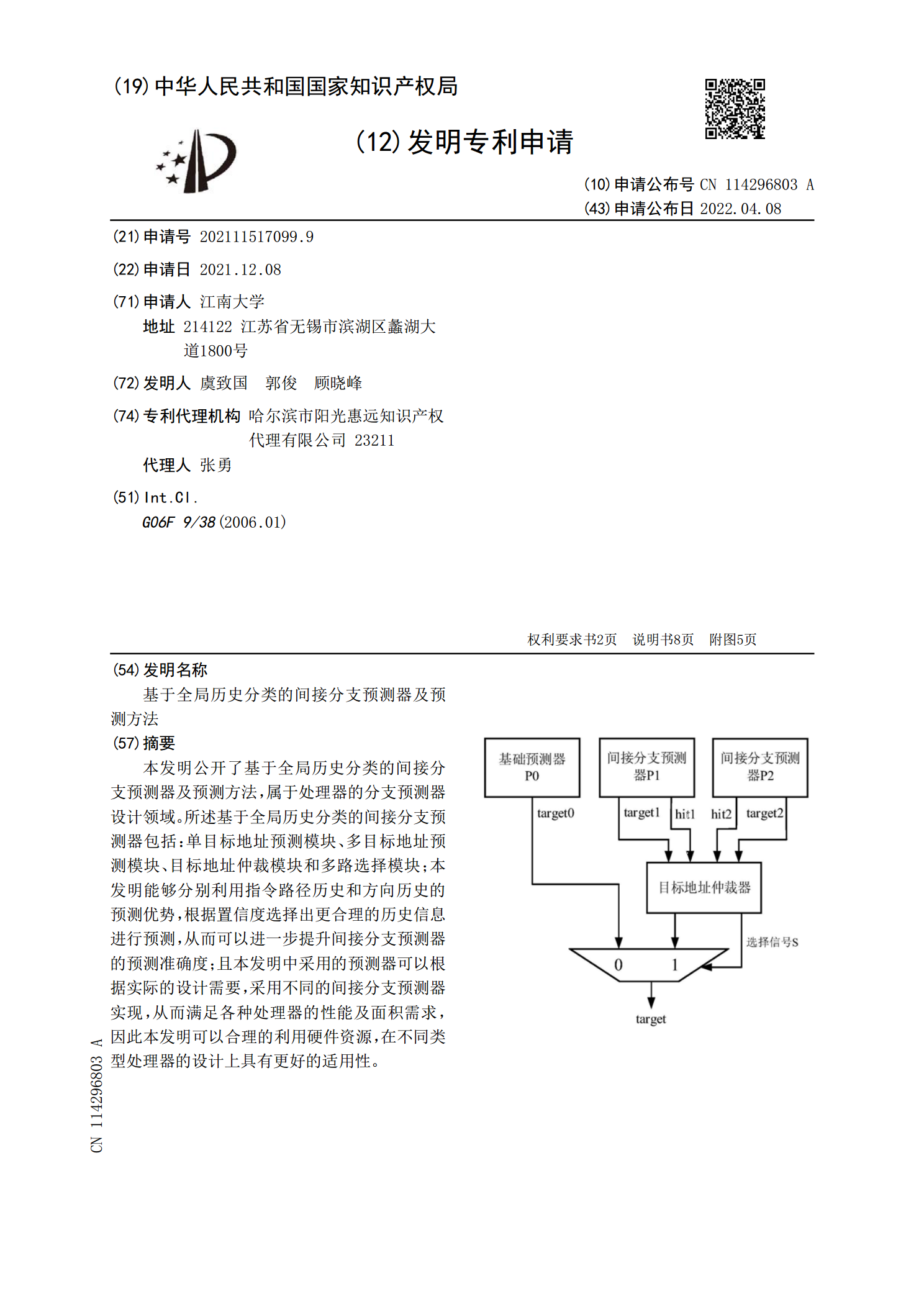

本发明公开了基于全局历史分类的间接分支预测器及预测方法,属于处理器的分支预测器设计领域。所述基于全局历史分类的间接分支预测器包括:单目标地址预测模块、多目标地址预测模块、目标地址仲裁模块和多路选择模块;本发明能够分别利用指令路径历史和方向历史的预测优势,根据置信度选择出更合理的历史信息进行预测,从而可以进一步提升间接分支预测器的预测准确度;且本发明中采用的预测器可以根据实际的设计需要,采用不同的间接分支预测器实现,从而满足各种处理器的性能及面积需求,因此本发明可以合理的利用硬件资源,在不同类型处理器的设计

推测执行处理器中分支指令与分支预测功能的验证方法.pdf

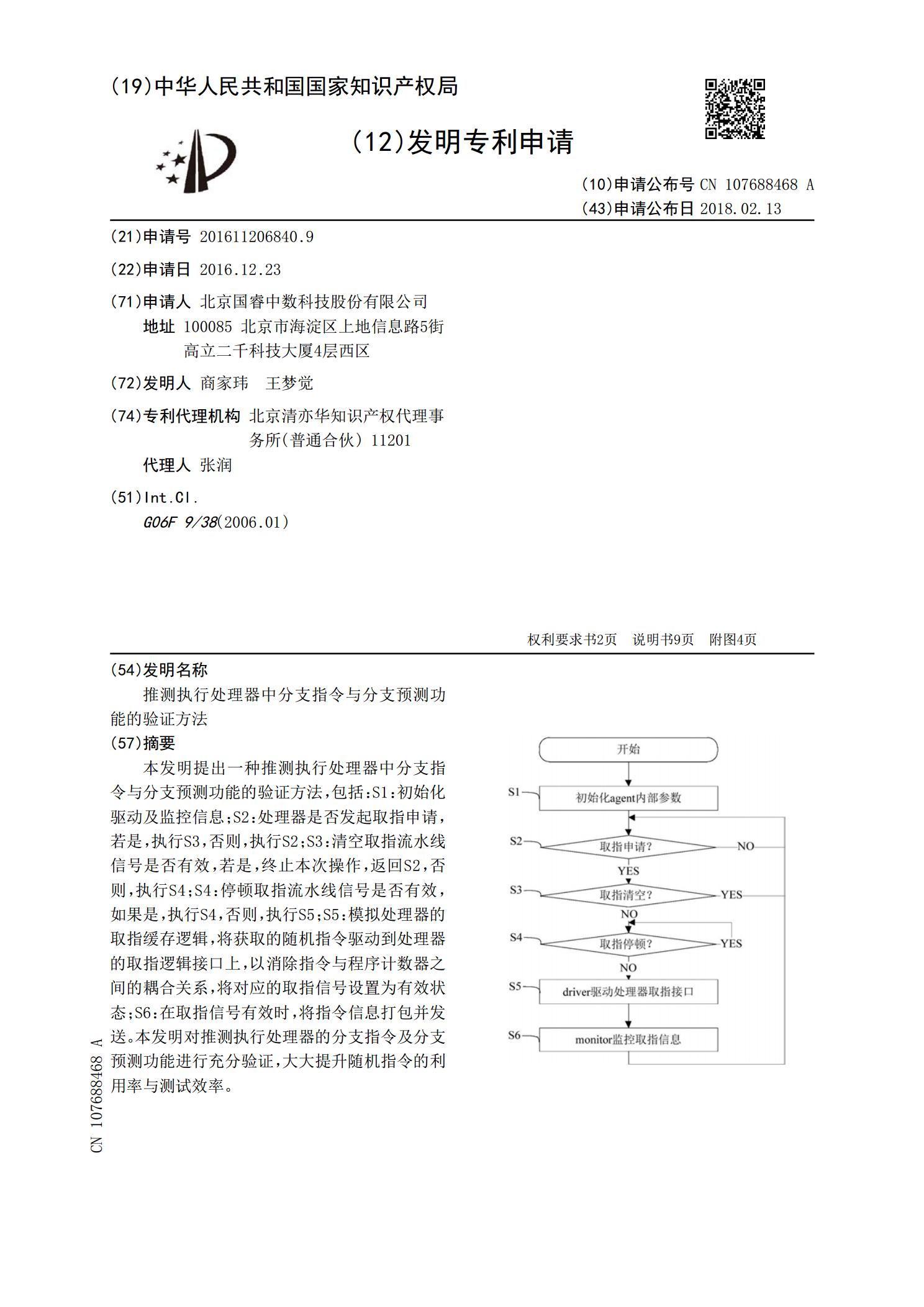

本发明提出一种推测执行处理器中分支指令与分支预测功能的验证方法,包括:S1:初始化驱动及监控信息;S2:处理器是否发起取指申请,若是,执行S3,否则,执行S2;S3:清空取指流水线信号是否有效,若是,终止本次操作,返回S2,否则,执行S4;S4:停顿取指流水线信号是否有效,如果是,执行S4,否则,执行S5;S5:模拟处理器的取指缓存逻辑,将获取的随机指令驱动到处理器的取指逻辑接口上,以消除指令与程序计数器之间的耦合关系,将对应的取指信号设置为有效状态;S6:在取指信号有效时,将指令信息打包并发送。本发明对