高对位精度的埋线路板制作方法.pdf

一条****88

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

高对位精度的埋线路板制作方法.pdf

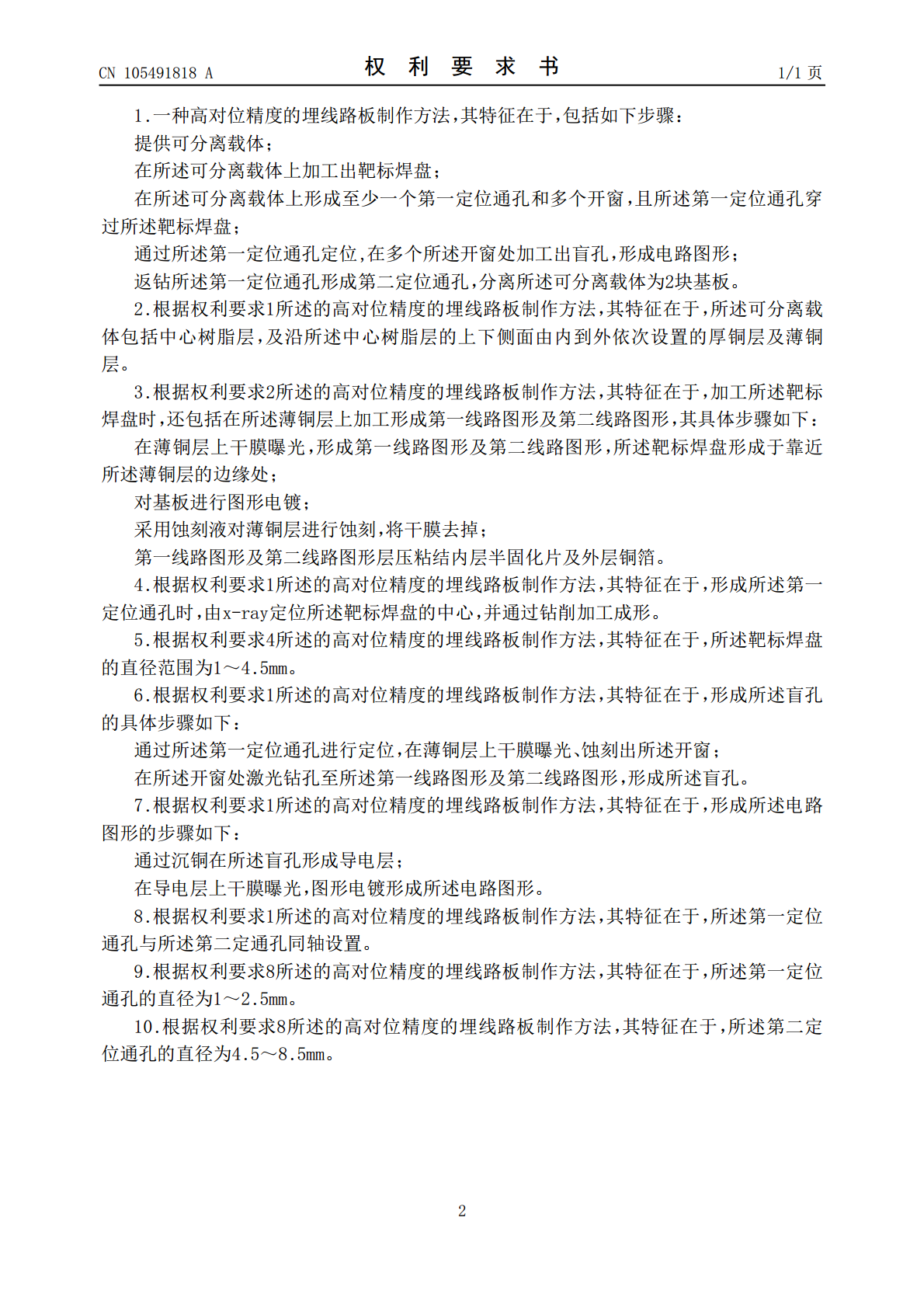

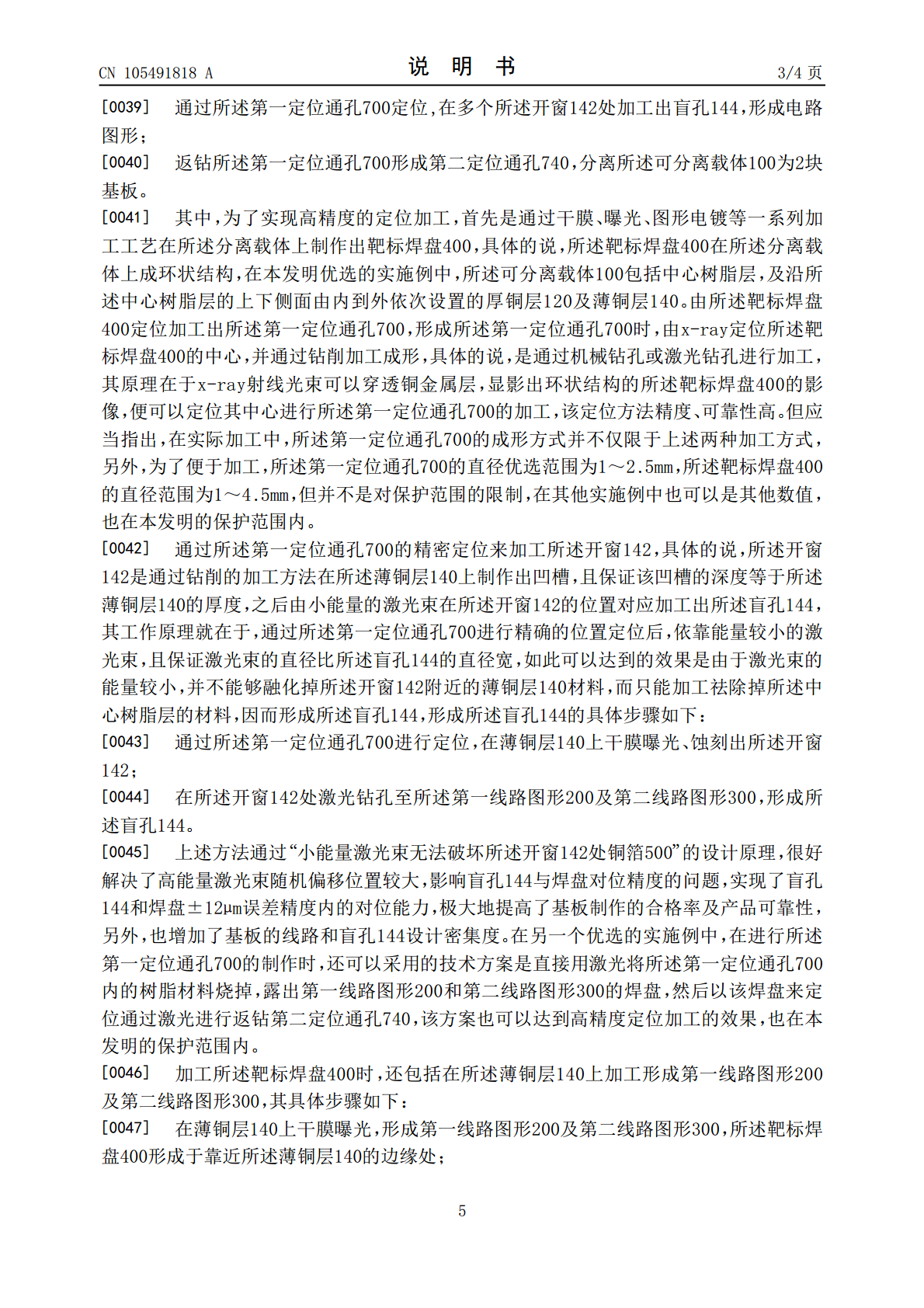

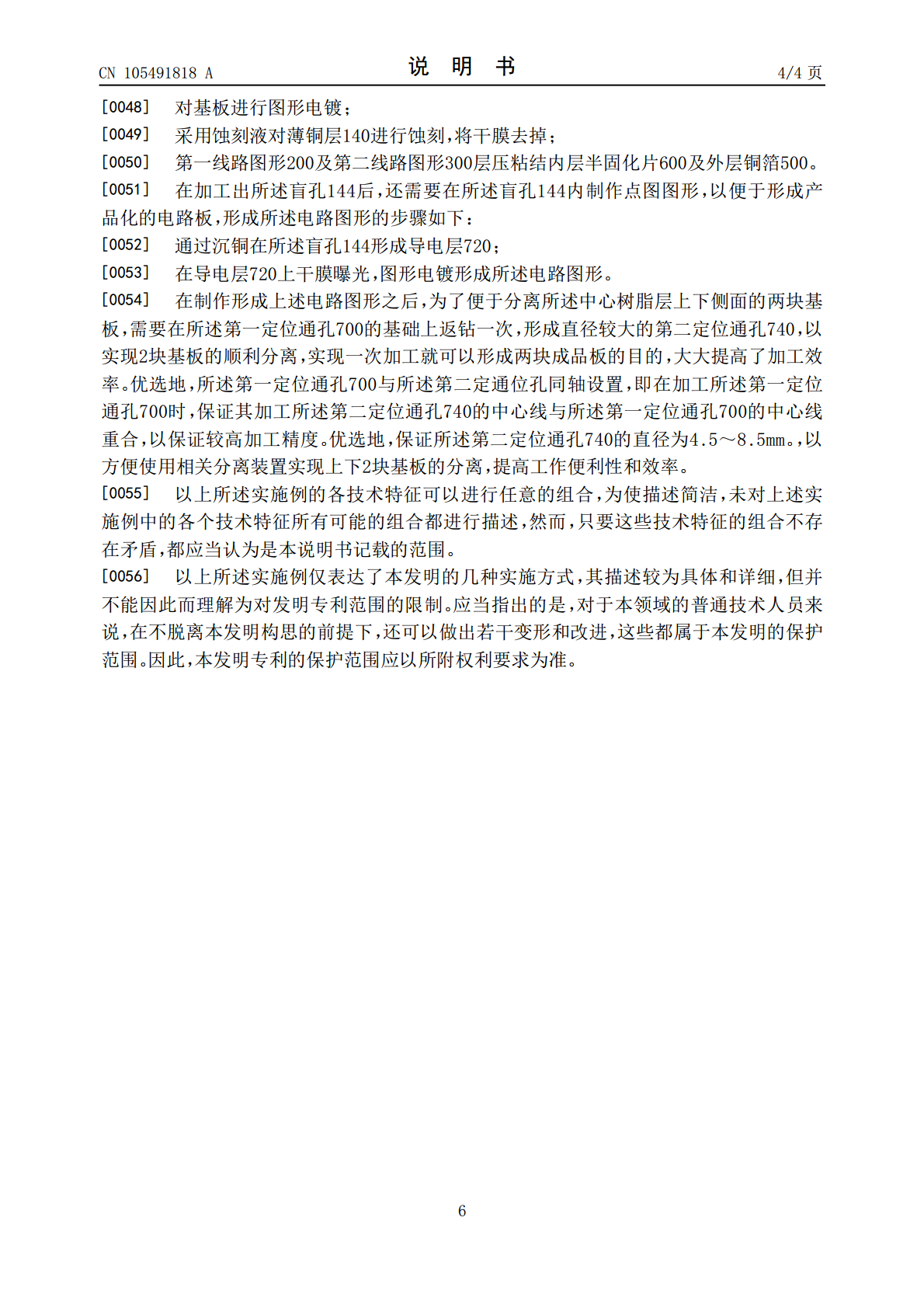

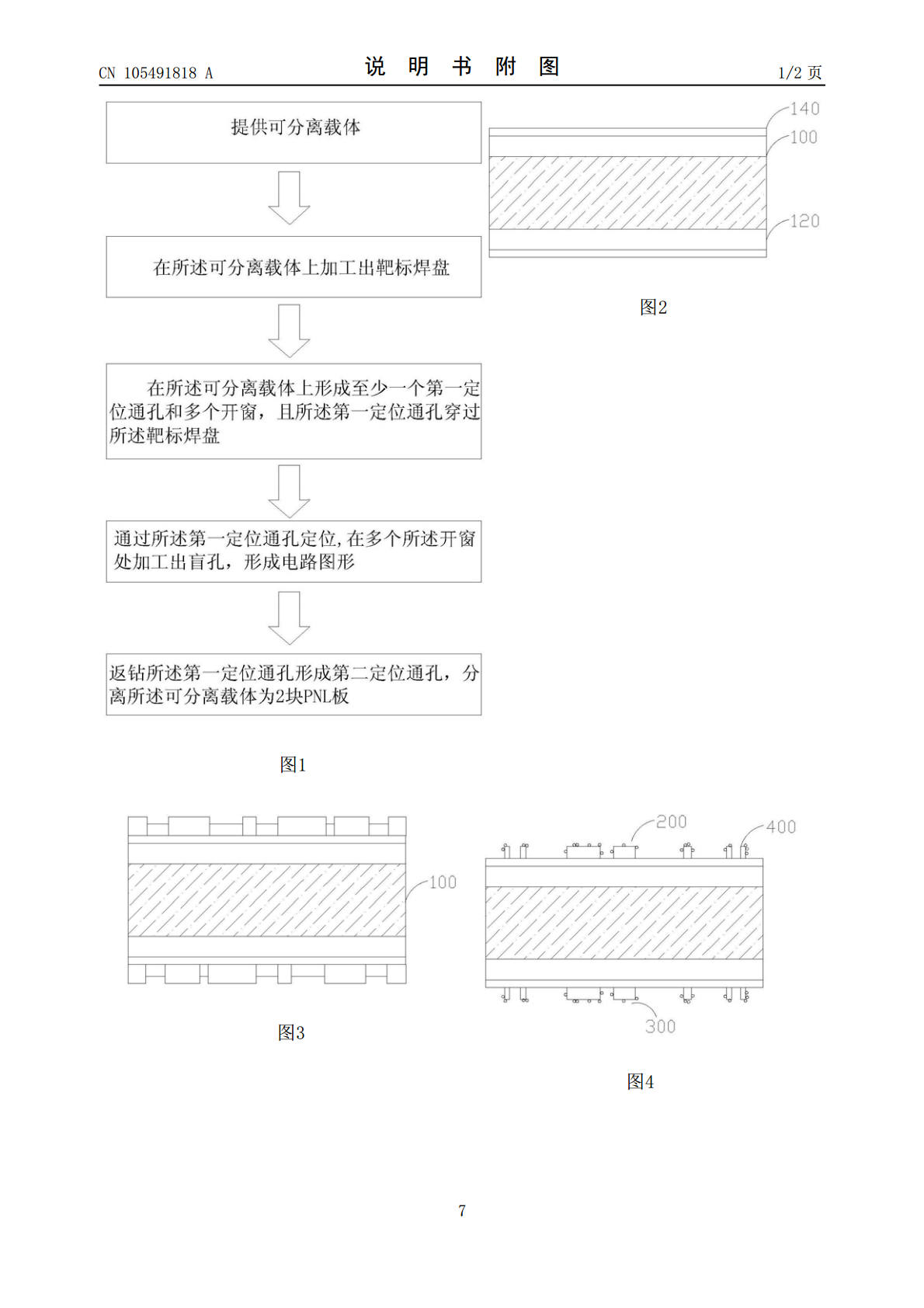

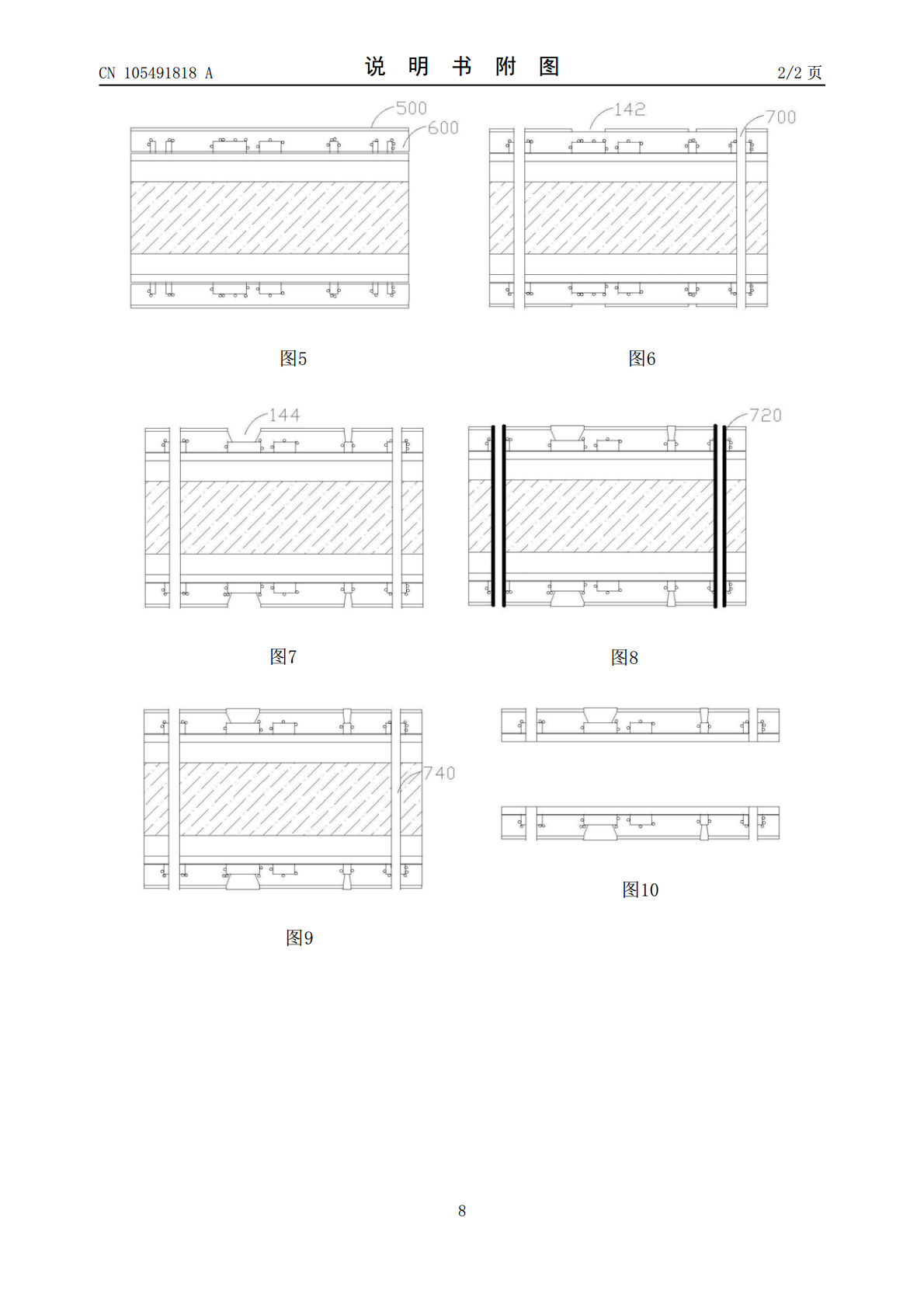

本发明公开了一种高对位精度的埋线路板制作方法,包括如下步骤:提供可分离载体;在所述可分离载体上加工出靶标焊盘;在所述可分离载体上形成至少一个第一定位通孔和多个开窗,且所述第一定位通孔穿过所述靶标焊盘;通过所述第一定位通孔定位,在多个所述开窗处加工出盲孔,形成电路图形;返钻所述第一定位通孔形成第二定位通孔,分离所述可分离载体为2块基板。很好解决了高能量激光束随机偏移位置较大,影响盲孔与焊盘对位精度的问题,实现了盲孔焊盘±12μm误差精度内的对位能力,极大地提高了基板制作的合格率及产品可靠性,另外,也增加了基

全自动线路板盲埋孔对位设备.pdf

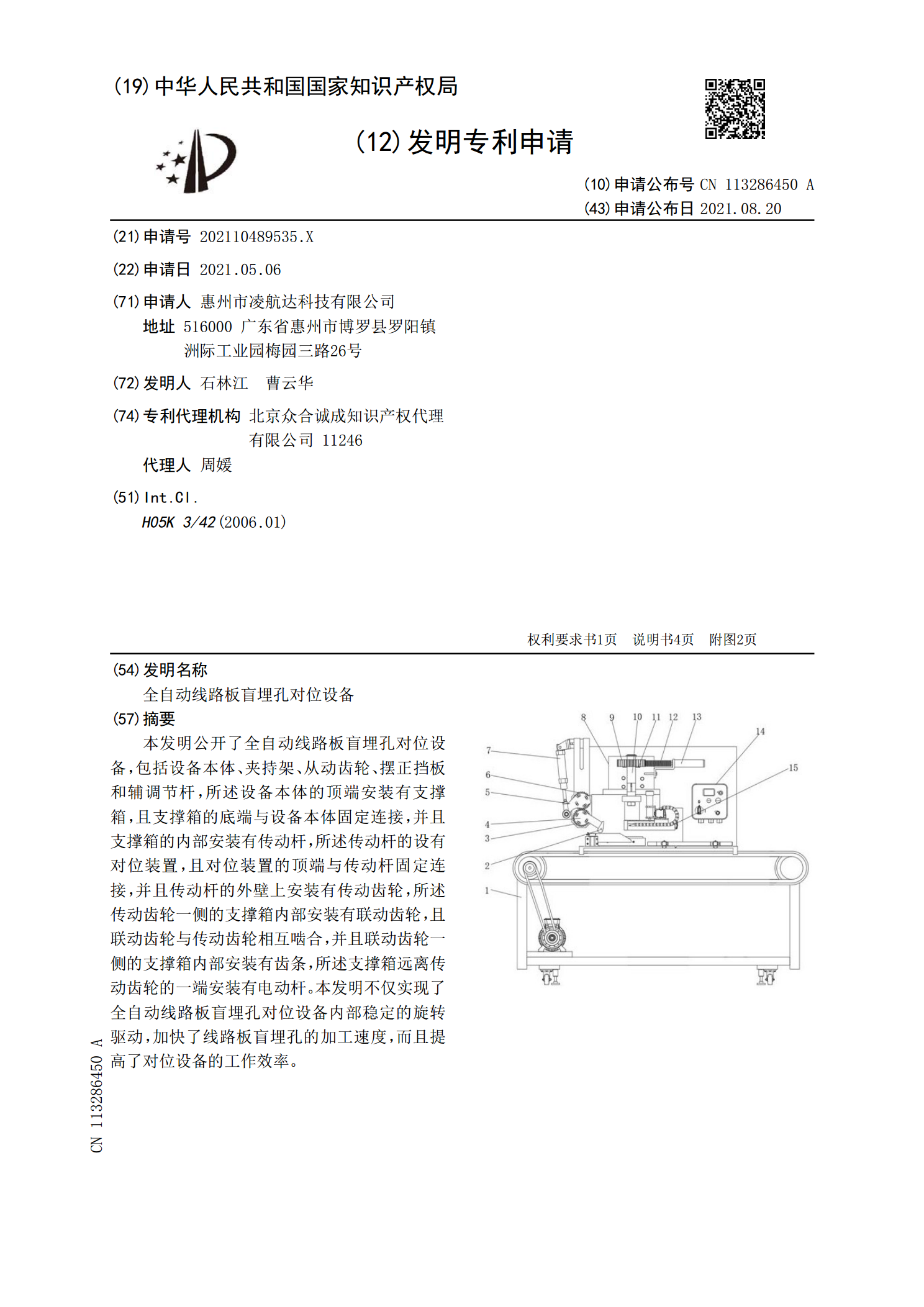

本发明公开了全自动线路板盲埋孔对位设备,包括设备本体、夹持架、从动齿轮、摆正挡板和辅调节杆,所述设备本体的顶端安装有支撑箱,且支撑箱的底端与设备本体固定连接,并且支撑箱的内部安装有传动杆,所述传动杆的设有对位装置,且对位装置的顶端与传动杆固定连接,并且传动杆的外壁上安装有传动齿轮,所述传动齿轮一侧的支撑箱内部安装有联动齿轮,且联动齿轮与传动齿轮相互啮合,并且联动齿轮一侧的支撑箱内部安装有齿条,所述支撑箱远离传动齿轮的一端安装有电动杆。本发明不仅实现了全自动线路板盲埋孔对位设备内部稳定的旋转驱动,加快了线路

一种提升印刷线路板对位精度的加工工艺.pdf

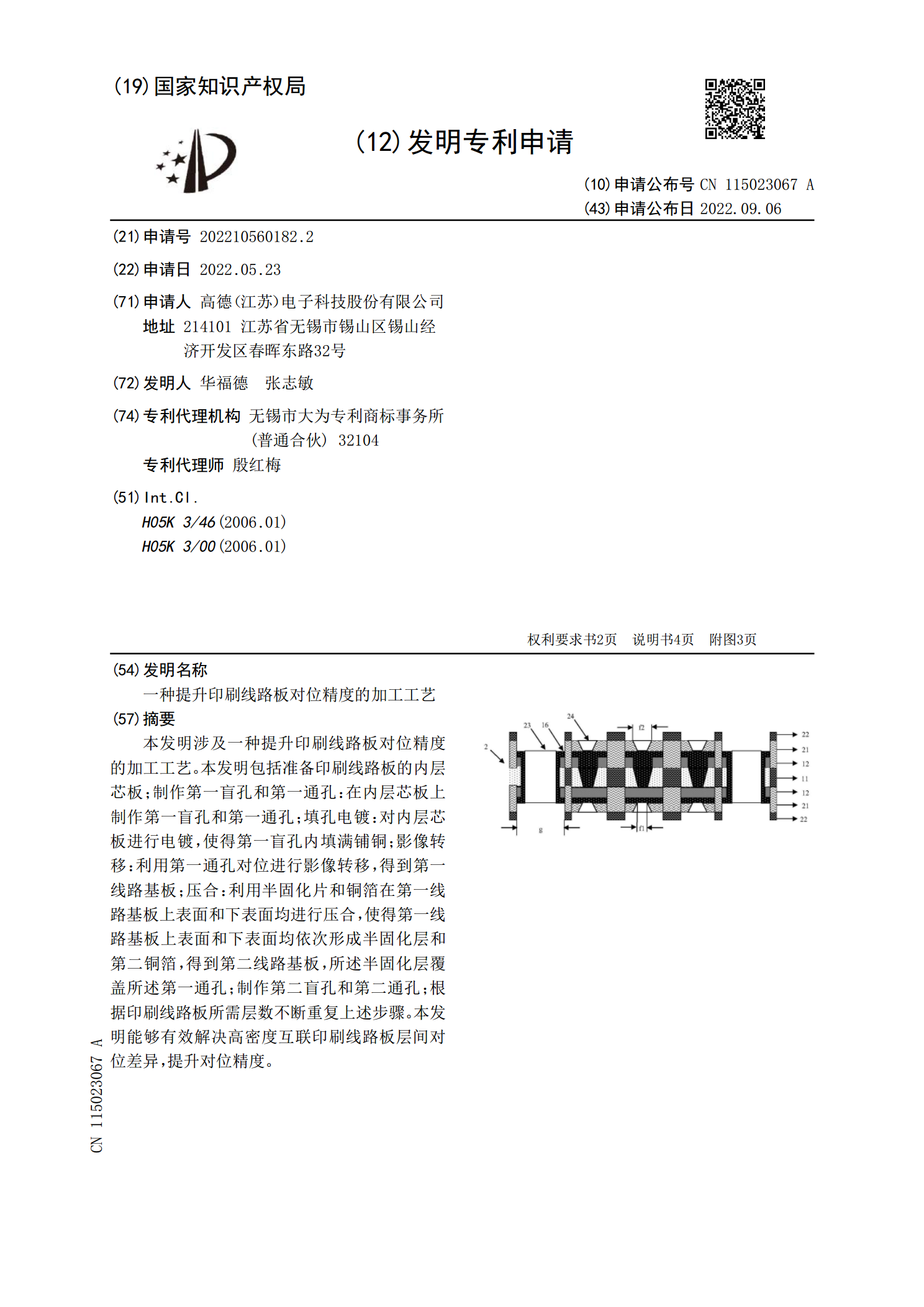

本发明涉及一种提升印刷线路板对位精度的加工工艺。本发明包括准备印刷线路板的内层芯板;制作第一盲孔和第一通孔:在内层芯板上制作第一盲孔和第一通孔;填孔电镀:对内层芯板进行电镀,使得第一盲孔内填满铺铜;影像转移:利用第一通孔对位进行影像转移,得到第一线路基板;压合:利用半固化片和铜箔在第一线路基板上表面和下表面均进行压合,使得第一线路基板上表面和下表面均依次形成半固化层和第二铜箔,得到第二线路基板,所述半固化层覆盖所述第一通孔;制作第二盲孔和第二通孔;根据印刷线路板所需层数不断重复上述步骤。本发明能够有效解决

一种提高多层线路板层间对位精度的方法.pdf

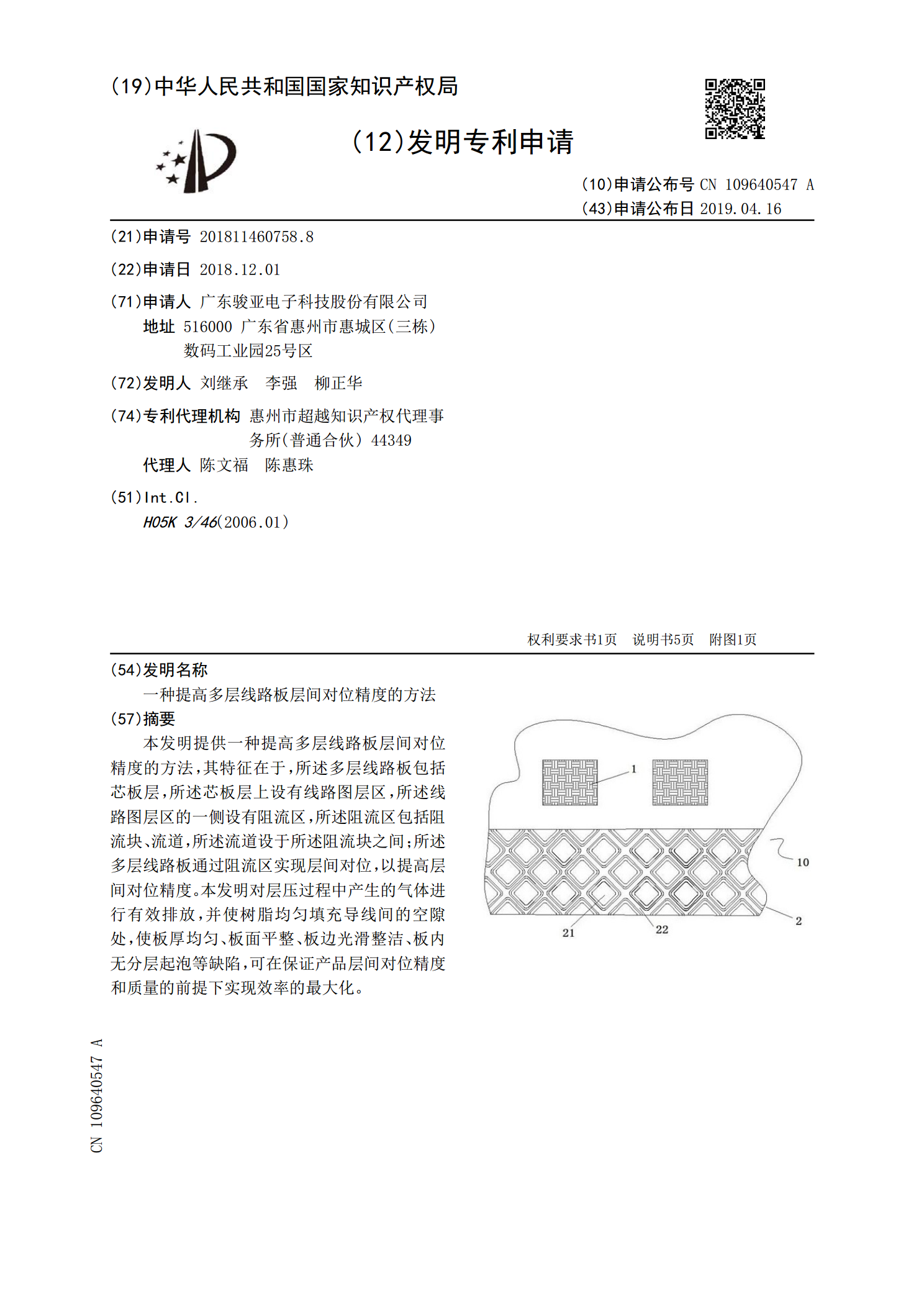

本发明提供一种提高多层线路板层间对位精度的方法,其特征在于,所述多层线路板包括芯板层,所述芯板层上设有线路图层区,所述线路图层区的一侧设有阻流区,所述阻流区包括阻流块、流道,所述流道设于所述阻流块之间;所述多层线路板通过阻流区实现层间对位,以提高层间对位精度。本发明对层压过程中产生的气体进行有效排放,并使树脂均匀填充导线间的空隙处,使板厚均匀、板面平整、板边光滑整洁、板内无分层起泡等缺陷,可在保证产品层间对位精度和质量的前提下实现效率的最大化。

高密度线路板对位孔及制作方法.pdf

本发明涉及一种高密度线路板对位孔,在所述高密度线路板图形区域周围设置多组对位孔,所述每组对位孔为多行多列的激光盲孔阵列,所述每组对位孔的激光盲孔之间采用导线串联连接以使每组激光盲孔阵列形成一个导电通路。本发明的对位孔,既能完成精确对位,又便于通过检测激光盲孔的导电检测激光盲孔的问题,从而提高了线路板制作的质量和效率。