半导体结构及其制造方法.pdf

Ch****75

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体结构及其制造方法.pdf

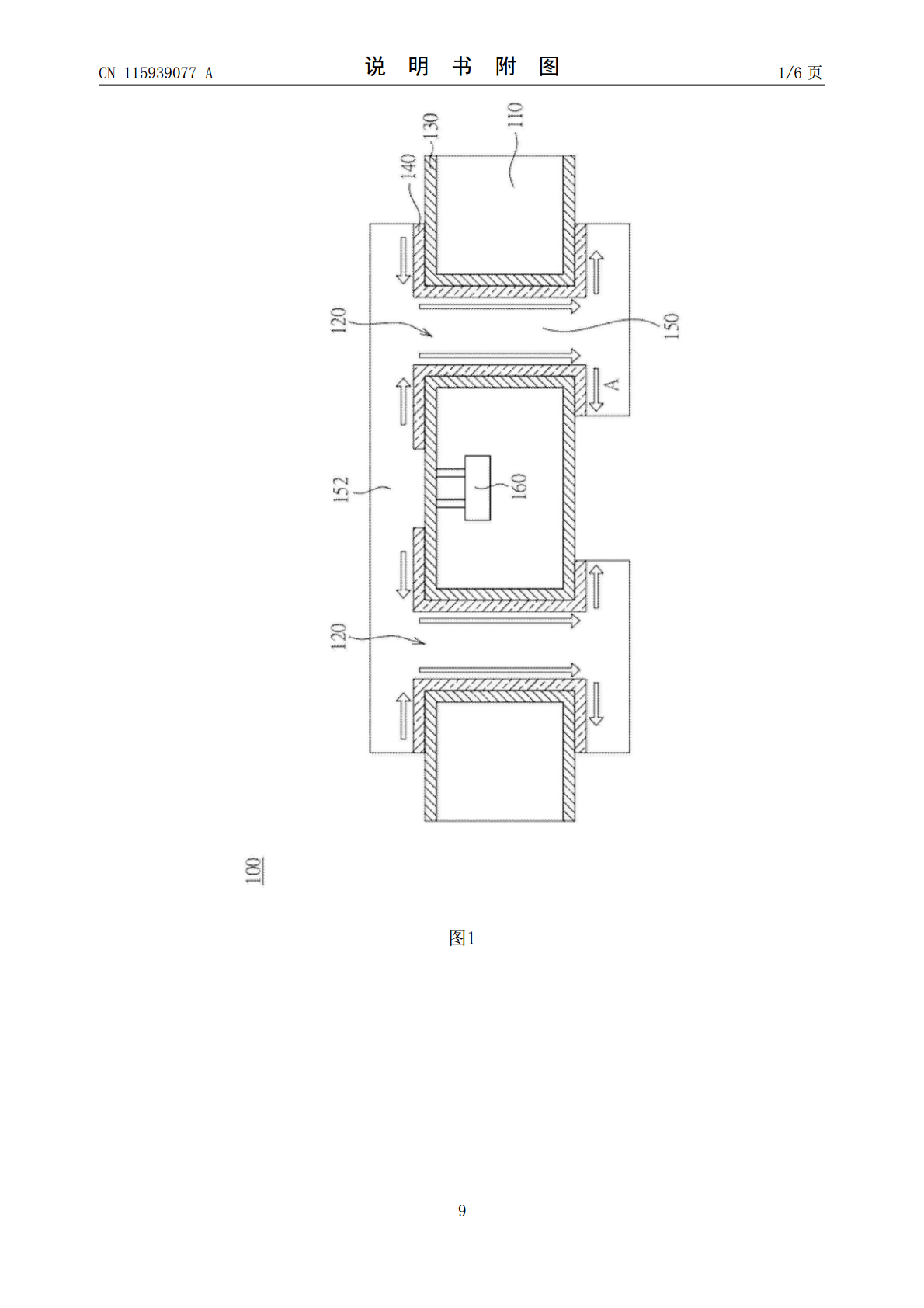

本申请实施例公开了一种半导体结构及其制造方法。所述半导体结构包括:半导体衬底;其中,所述半导体衬底中具有沟槽,所述沟槽中形成有栅极;掺杂层,所述掺杂层位于所述沟槽外侧的所述半导体衬底中;在垂直于所述半导体衬底的方向上,所述掺杂层包括:过渡层和位于所述过渡层上的离子注入层;所述过渡层的掺杂浓度小于所述离子注入层的掺杂浓度;在垂直于所述半导体衬底的方向上,所述过渡层的顶表面不低于所述栅极的底表面。

半导体结构及其制造方法.pdf

本公开的实施例提供了一种形成半导体结构的方法,包括:提供包括第一电路区域和第二电路区域的衬底;在衬底上形成半导体堆叠件,其中,半导体堆叠件包括交替堆叠在衬底上的具有第一成分的第一半导体层和具有第二成分的第二半导体层;对半导体堆叠件和衬底执行第一图案化工艺,以形成具有第一深度的第一沟槽;对半导体堆叠件和衬底执行第二图案化工艺,以在第一电路区域中形成具有第二深度的第二沟槽并在第二电路区域中形成具有第三深度的第三沟槽,第三深度小于第二深度。本公开的实施例还提供了一种半导体结构。

半导体结构及其制造方法.pdf

提供了半导体结构及其制造方法。半导体结构包括衬底和形成在衬底上方的底部隔离部件。半导体结构还包括形成在底部隔离部件上方的底部半导体层和形成在底部半导体层上方的纳米结构。半导体结构还包括连接到纳米结构并且覆盖底部隔离部件的部分的源极/漏极结构。

半导体结构及其制造方法.pdf

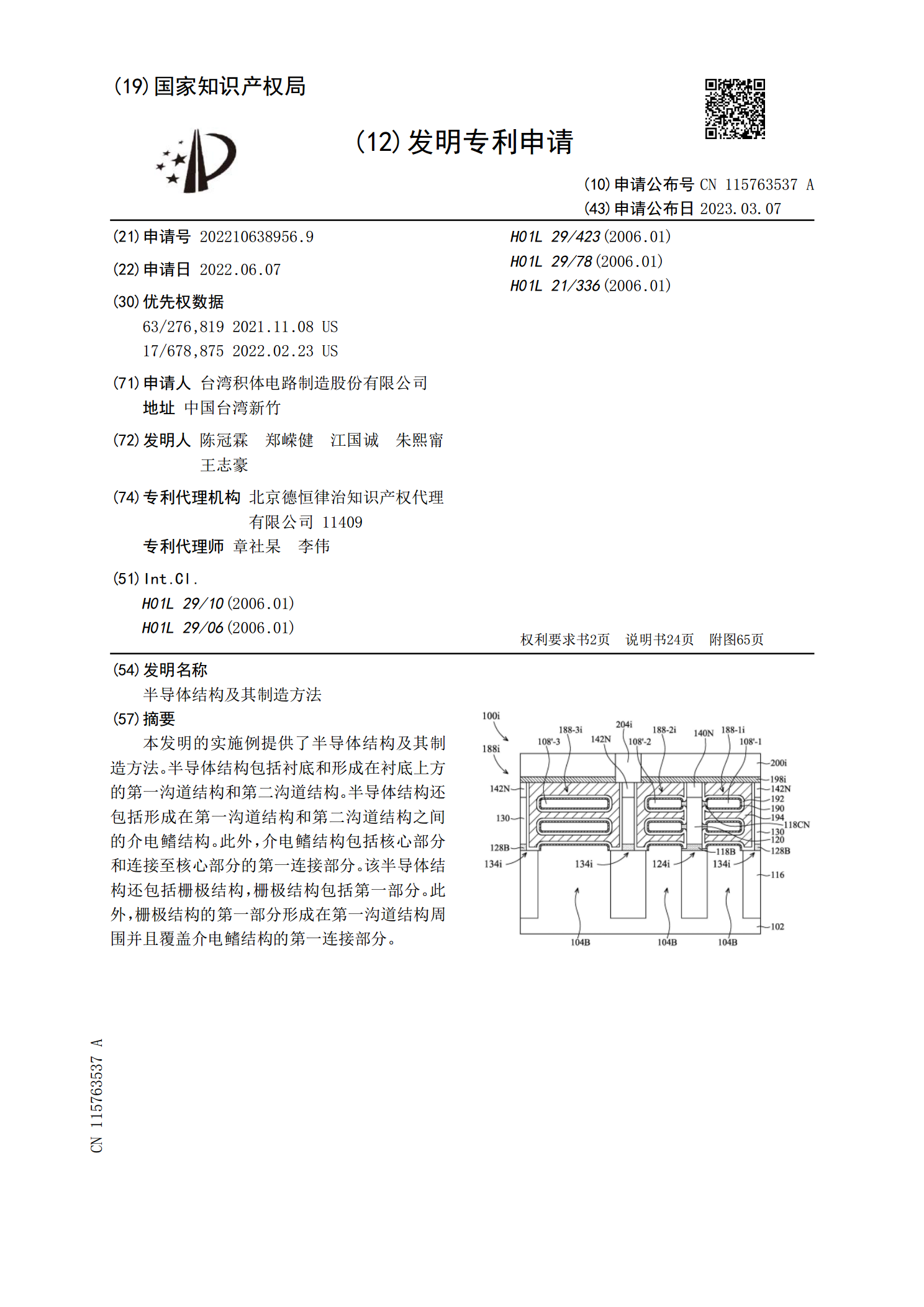

本发明的实施例提供了半导体结构及其制造方法。半导体结构包括衬底和形成在衬底上方的第一沟道结构和第二沟道结构。半导体结构还包括形成在第一沟道结构和第二沟道结构之间的介电鳍结构。此外,介电鳍结构包括核心部分和连接至核心部分的第一连接部分。该半导体结构还包括栅极结构,栅极结构包括第一部分。此外,栅极结构的第一部分形成在第一沟道结构周围并且覆盖介电鳍结构的第一连接部分。

半导体结构及其制造方法.pdf

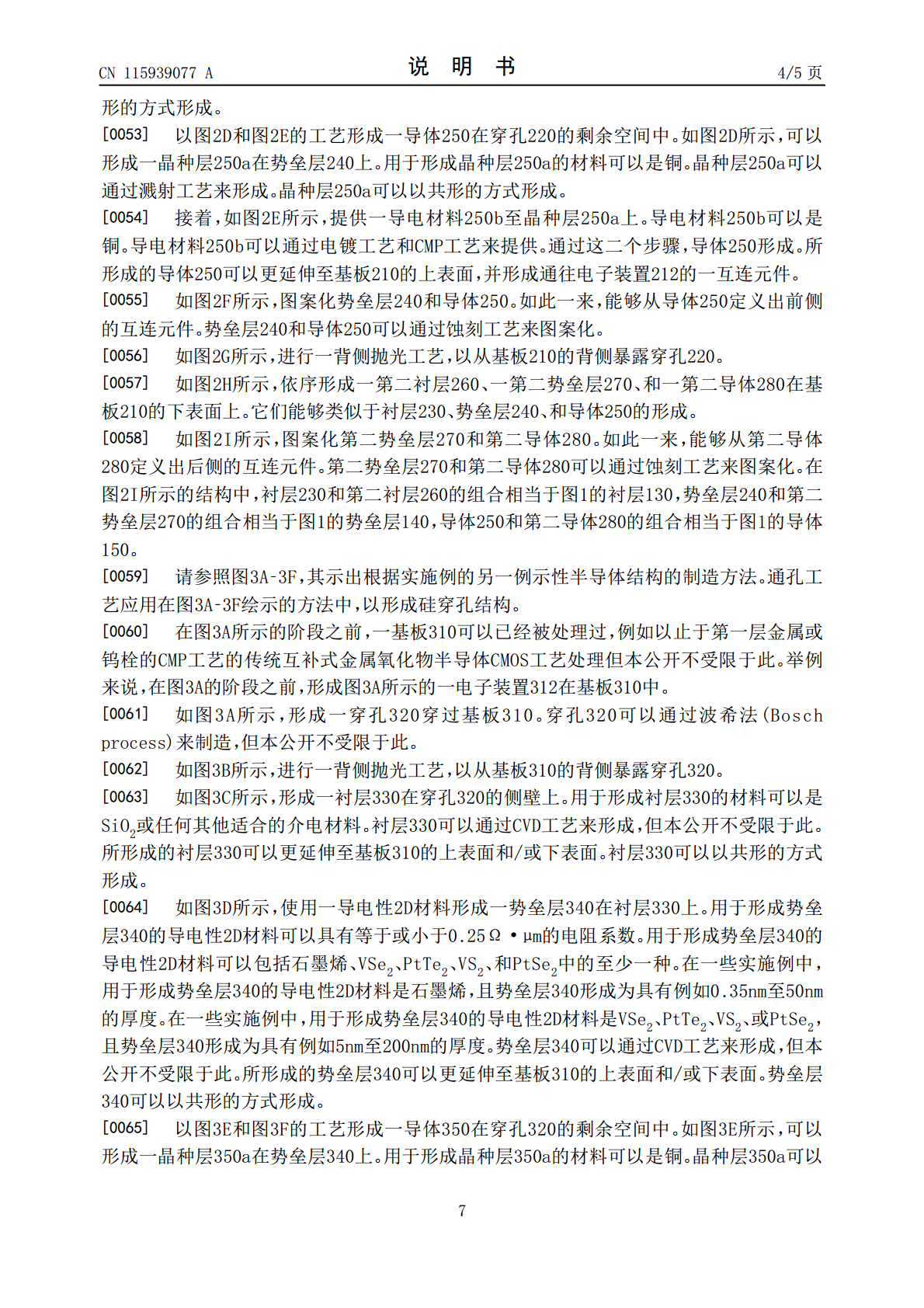

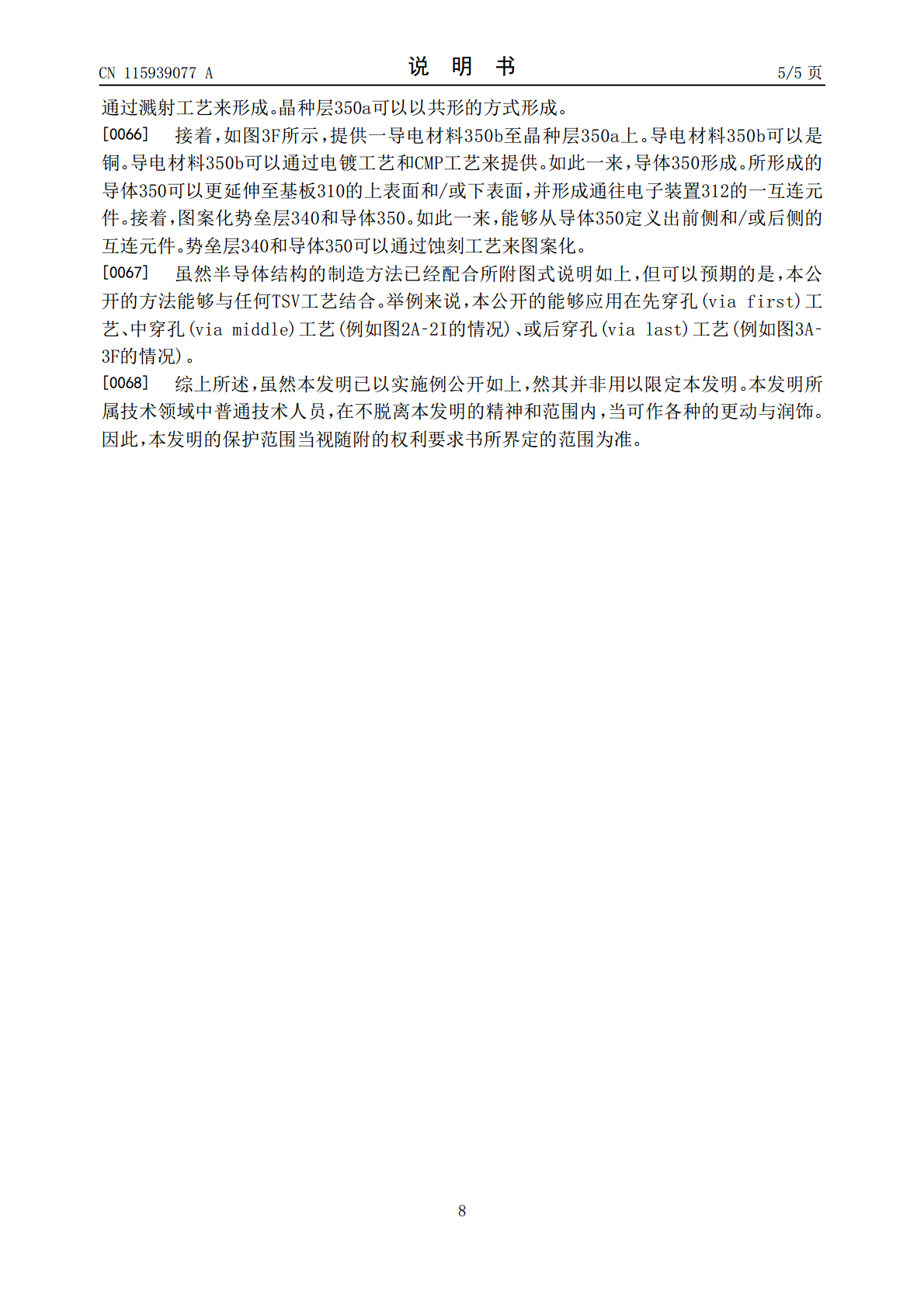

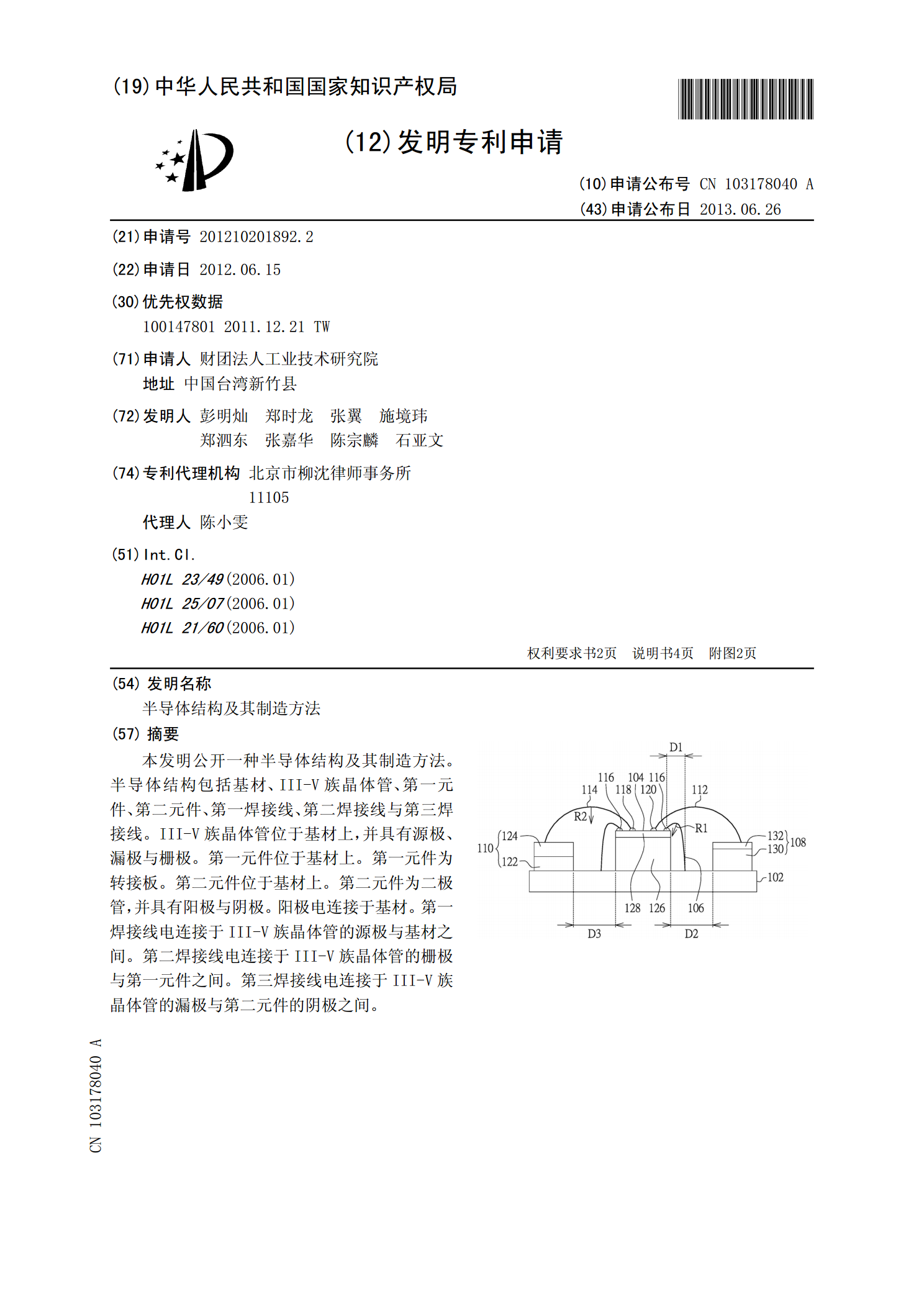

本发明公开一种半导体结构及其制造方法。半导体结构包括基材、III-V族晶体管、第一元件、第二元件、第一焊接线、第二焊接线与第三焊接线。III-V族晶体管位于基材上,并具有源极、漏极与栅极。第一元件位于基材上。第一元件为转接板。第二元件位于基材上。第二元件为二极管,并具有阳极与阴极。阳极电连接于基材。第一焊接线电连接于III-V族晶体管的源极与基材之间。第二焊接线电连接于III-V族晶体管的栅极与第一元件之间。第三焊接线电连接于III-V族晶体管的漏极与第二元件的阴极之间。